Устройство для контроля блока постоянной памяти

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 1н1 514349

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Саюэ Советских

Социалистических

Республик(61) Дополнительное к авт. свпд-ву (22) Заявлено 16.01.75 (21) 2097150/24 с присоединением заявки № (51) М. Кл е 6 11С 29/00

Совета Министров СССР по делам изобретений н открытий (53) УДК 681.327(088.8) Опубликовано 15.05.76. Бюллетень № 18

Дата опубликования описания 20.07.76 (72) Авторы изобретения

А. В. Тимашев, А. А. Борискин и А. H. Пресняков (71) Заявитель

Особое конструкторское бюро вычислительной

Рязанского радиотехнического институт е

--. (54) УСТРОИСТВО

ДЛЯ КОНТРОЛЯ БЛОКА ПОСТОЯ HНО И ПАМЯТИ

Государственный комитет (23) Приоритет

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля блока постоянной памяти, содержащее регистр, выходы которого соединены со входами блока сравнения, блок установки контрольной суммы и блок управления.

С целью увеличения быстродействия, предложенное устройство отличается тем, что оно содержит регистр сдвига, входы которого подключены к выходам блока установки контрольной суммы, а выходы — ко входам блока сравнения, и элемент «И», входы которого соединены с одной из входных шин устройства и выходом блока управления, а выход — с управляющим входом регистра сдвига.

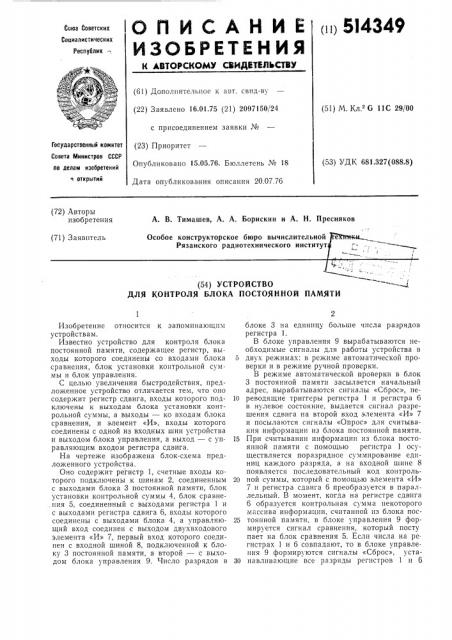

На чертеже изображена блок-схема предложенного устройства.

Оно содержит регистр 1, счетные входы которого подключены к шинам 2, соединенным с выходами блока 3 постоянной памяти, блок установки контрольной суммы 4, блок сравне, ния 5, соединенный с выходами регистра 1 и с выходами регистра сдвига 6, входы которого соединены с выходами блока 4, а управляющий вход соединен с выходом двухвходового элемента «И» 7, первый вход которого соединен с входной шиной 8, подключенной к блоку 3 постоянной памяти, а второй — с выходом блока управления 9. Число разрядов в блоке 3 на единицу больше числа разрядов регистра 1.

В блоке управления 9 вырабатываются необходимые сигналы для работы устройства в

5 двух режимах: в режиме автоматической проверки и в режиме ручной проверки.

В режиме автоматической проверки в блок

3 постоянной памяти засылается начальный адрес, вырабатываются сигналы «Сброс», пе10 реводящие триггеры регистра 1 и регистра 6 в нулевое состояние, выдается сигнал разрешения сдвига на второй вход элемента «И» 7 и посылаются сигналы «Опрос» для считывания информации из блока постоянной памяти.

15 При считывании информации из блока постоянной памяти с помощью регистра 1 осуществляется поразрядное суммирование единиц каждого разряда, а на входной шине 8 появляется последовательный код контроль20 ной суммы, который с помощью элемента «И»

7 и регистра сдвига 6 преобразуется в параллельный. В момент, когда на регистре сдвига

6 образуется контрольная сумма некоторого массива информации, считанной из блока пос25 тоянной памяти, в блоке управления 9 формируется сигнал сравнения, который посту пает на блок сравнения 5. Если числа на ре гистрах 1 и 6 совпадают, то в блоке управления 9 формируются сигналы «Сброс», уста30 навливающие все разряды регистров 1 и 6

514349

Формула изобретения

Составитель В. Рудаков

Редактор Л. Тюрина Техред А. Камышникова Корректор А. Овчинникова

Заказ 2025/11 Изд. Мв 1438 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий!

13035, Москва, Ж-35, Раушская наб., д. 475

Типография, пр, Сапунова, 2 в «нулевое» состояние, вновь формируются сигналы опроса блока постоянной памяти и осуществляются считывание следующего массива информации из блока постоянной памяти и его проверка. После того, как будет проверен весь объем информации блока постоянной памяти, цикл испытаний повторяется, одновременно сигнализируя оператору о том, что он прошел успешно. Если же с приходом из блока управления 9 сигнала сравнения числа на регистрах 1 и 6 неравны, то вырабатывается сигнал останова, свидетельствующий, что при считывании данного массива информации произошла ошибка, и блок управления

9 переводится в режим ручной проверки. При этом вырабатывается сигнал, запрещающий прохождение сигналов, поступающих на шину

8, через элемент «И» 7 по индикации блока управления 9 определяется адрес блока постоянной памяти, начиная с которого осуществляется неверное считывание информации из блока постоянной памяти. Место ошибки находится последовательным изменением диапазона адресов, начиная с указанного адреса, при этом каждый раз вручную в блоке4устанавливается своя контрольная сумма.

Устросйтво для контроля блока постоянной

10 памяти, содержащее регистр, выходы которого соединены со входами блока сравнения, блок установки контрольной суммы и блок управления, отл ич а ющееся тем, что, с целью увеличения быстродействия устройства, I5 оно содержит регистр сдвига, выходы которого подключены к выходам блока установки контрольной суммы, а выходы — ко входам блока сравнения, и элемент «И», входы которого соединены с одной из входных шин устройства

20 и выходом блока управления, а выход — с управляющим входом регистра сдвига.