Реверсивный делитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАЙ ЙЕ

ИЗОБРЕТЕНИЯ (i i1 5l 4443

Свив Советских

Социавмотичвоких

Рввпуолик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 20,05.74 (21) 2025714/21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 15.05.76. Бюллетень № 18

Дата опубликования описания 22.06.76 (51) М. Кл,"- H 03K 23, 02

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374.44 (088.8) (72) Автор изобретения

B. И. Кочергин (71) Заявитель (54) PEBEPCHBHbiA ДЕЛИТЕЛЬ ЧАСТОТЬ!

Изобретение относится к импульсной технике, в частности к реверсивным делителям частоты, которые могут также служить счетчиками импульсов в двси пном коде и используется в электропрпводах переменного и постоянного тока, устройствах автоматики и вычислительной техники.

Известен ревсрсивный делитель частоты, содержащий каналы деления, каждый нз каналов состоит из кольцевого делителя частоты, каждый разряд которого выполнен на двух триггерах.

Однако извсстное устройство пе обладает высокой надежностью работы.

С целью повышения надежности работы устройства в каждый канал деления введены четыре элемента И и два элемента ИЛИ, к входам которых попарно подключены выходы элементов И, при этом входы первого элемента И подключены к инверсным выходам триггеров каждого разряда кольцевого делителя частоты, выходы второго элемента И— к прямым выходам триггеров, входы третьего элемента И вЂ” к инверсному выходу первого и к прямому выходу второго триггеров, входы четвертого элемента И вЂ” к прямому выходу первого и к инверсному выходу второго упомянутых триггеров каждого разряда кольцевого делителя частоты.

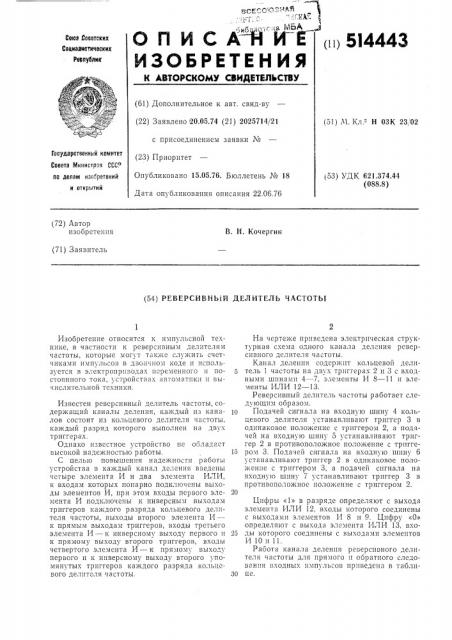

На чертеже приведена электрическая структурная схема одного канала деления реверсивного делителя частоты.

Канал деления содержит кольцевой делитель 1 частоты на двух триггерах 2 п 3 с входными шинами 4 — 7, элементы И 8 — 11 и элементы ИЛИ 12 — 13.

Реверсивный делитель частоты работает следующим образом.

10 Подачей сигнала на входную шину 4 кольцевого делителя устанавливают триггер 3 в одинаковое положение с триггером 2, а подачей на входную шину 5 устанавливают триггер 2 в противоположное положение с трпгге15 ром 3. Подачей сигнала на входную шину 6 устанавливают триггер 2 в одинаковое положение с триггером 3, а подачей сигнала на входную шину 7 устанавливают триггер 3 в противоположное положение с триггером 2.

Цифры «1» в разряде определяют с выхода элемента ИЛИ 12, входы которого соединены с выходами элементов И 8 и 9. Цифру «О» определяют с вы ода элемента ИЛИ 13, вхо25 ды которого соединены с выходами элементов

И10п11.

Работа канала деления реверсивного делителя частоты для прямого и обратного следования входных импульсов приведена в таблпЗО це.

514443

Сигналы триггеров

Выходные сигналы элементов И

Цифры

8 9 10 11

0

„1"

„0"

„0"

При следовании импульсов на входные шины 4, 6, 5, 7 первый импульс поступает на входную шину 4 и устанавливает триггер 3 в одинаковое положение с триггером 2. В делителе разряда записана цифра «1», а на выходе элемента И 9 появляется сигнал. Следующий импульс поступает на входную шину 6 для установки триггера 2 в одинаковое поло>кение с триггером 3, однако переключения нет, так как триггеры уже находятся в одинаковом положении.

Следующий по порядку импульс поступает на входную шину 5 и устанавливает триггер 2 в противоположное положение с триггером 3.

В разряде делителя дана цифра «О» и на выходе элемента И 10 появляется сигнал.

При поступлении на входную шину 7 импульса для установки триггера 3 в противоположное положение с триггером 2 схема не переключается, так как они уже установлены в противоположное положение и т. д.

Следовательно, переключение в схеме разряда происходит только при поступлении импульсов на входные шины 4 и 5, а на выходе появляются периодически цифры «1» и «О», что соответствует режиму суммирования.

В это время на выходах элементов И 8 и 10, 9 и 11 появляются сигналы в последовательности входных импульсов, но с частотой в два раза ниже.

При поступлении входных импульсов на входные шины 7, 5, 6, 4 первыми импульсами, 5 которые производят переключение в схеме, являются импульсы, поступающие на входные шины 7 и 6, а импульсы, поступающие на входные шины 4 и 5, переключений не вызывают, поэтому переключение происходит в со10 ответствии с таблицей снизу вверх, и на выходе периодически появляются цифры «О» и «1», что соответствует режиму вычитания, при этом на выходах элементов И 9, 10, 8 и 11 появляются сигналы в последовательности вход15 ных импульсов, но с частотой в два раза ниже.

Формула изобретения

Реверсивный делитель частоты, содержащий каналы деления, каждый из каналов состоит из кольцевого делителя частоты, каждый разряд которого выполнен на двух триггерах, о т25 личающийся тем, что, с целью повышения надежности работы устройства, в каждый канал деления введены четыре элемента И и два элемента ИЛИ, к входам которых попарно подключены выходы элементов И, при этом входы первого элемента И подключены к инверсным выходам триггеров каждого разряда кольцевого делителя частоты, выходы второго элемента И вЂ” к прямым выходам триггеров, входы третьего элемента И вЂ” к инверсному выходу первого и к прямому выходу второго триггеров, входы четвертого элемента И вЂ” к прямому выходу первого и к инверсному выходу второго триггеров каждого разряда кольцевого делителя частоты.

Редактор T. Янова

Составитель М. Аудринг

Техред Т. Курилко

Корректор Т. Гревцова

Заказ 1359/4 Изд. М 1375 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2