Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (1 1) 515151 (61) Дополнительное к авт. свид-ву (22) Заявлено 15.01.75(21) 2097136/24 с присоединением заявки №вЂ” (23) Приоритет (51) М. Кл.2 С 11с 11/00

Гасударственный номитет

Совета Министров СССР но делам изооретений и открытий (43) Опубликовано25.05.76.Бюллетень ¹19 (53) УДК 681.327. 6

1 (088. 8) Л. А. Шумилов, В. Н. Гебгарт и А. О. Тимофеев (72) Авторы изобретения

Ленинградский ордена Ленина электротехнический институт им.

В. И. Ульянова (Ленина) (71) Заявитель (54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Известно запоминающее устройство, содержащее накопитель, собранный на транзис=орах и ферритовых сердечниках, прошитых выходными шинами, подключенными к усилителям считывания, числовыми шинами считывания, одни концы которых соединены с коллекторами соответствующих транзистсров, к эммитерам которых подключены разрядные шины, а к базам - числовые шины записи — считывания, соединенные с одним 1р из дешифраторов адреса.

Недостатком известного устройства является б ольш ое количеств о шин, прошивающих сердечники. 15

В предлагаемом устройстве другие концы числовых шин считывания подключены к выходам другого дешифратора адреса.

Такое конструктивное решение обеспечивает работу транзистора запоминающего 20 элемента при считывании в прямом режиме, а при записи — в инвертном. Это позволяет сократить число шин, прошивающих каждый ферритовый сердечник устройства, до двух.

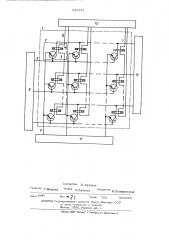

На чертеже представлена электрическая р схема накопителя предлагаемого устройства вместе с блоком электронного обрамления.

Запоминающее устройство содержит накопитель 1 с запоминающими элементами 2, содержащими транзистор 3 и ферритовый сердечник 4 с прямоугольной петлей гистерезиса:, числовые шины записи-считывания

5, которые подключены к базам транзисторов З„разрядные шины 6, к которым подключены эммитеры транзисторов 3; числовые шины считывания 7, одни концы которых подключены к выводам коллекторов транзисторов 3, которые, в свою очередь, прошивают ферритовые сердечники 4; выходные шины 8, прошивающие ферритовые сердечники 4„первый дешифратор адреса 9, подключенный к числовым шинам записи — считывания 5; второй дешифратор адреса 10, подключенный к другим концам числовых шин считывания 7; блок 11 разрядных формирователей, подключенный к разрядным шинам Д„ усилители считывания 12, подключенные к выходным шинам 8.

Устройство может работать в одном из двух режимов: "считывание или "запись"

515151 нуля или единицы. При работе устройства в режиме "считывание" на выходе первого дешифратора адреса 9, соответствующего выбранному для считывания числу, появляется импульс напряжения, подаваемый в 5 соответствующую числовую шину записи-счить>вания 5, на выходе второго дешифратора адреса 10, соответствующего тому же числу, и оявляется импульс напряжения, п одаваемый в соответствующую числовую шину 1О считывания 7. На всех выходах блока 11, разряднь,х формирователей, подключенных к разрядным шинам 6, установлен нулевой уровень напряжения, Тем самым обеспечивается протекание токов считыван вания через запоминающие элементы 2 выбранного числа, причем транзисторы этих запоминающих элементов раб отают в прям ом режиме. Сигналы считанных единиц, наведенные в выходных шинах 8, поступают в усилители считы- о вания 12. На прочих выходах первого и второго дешифраторов адреса 9 и 10 сохраняется нулевой уровень напряжения, и токи считывания в шинах остальных чисел не протекают, 25

При работе в режиме "запись" на выходе первого дешифратора адреса 9, соответствующегo выбранному числу, появляется импульс напряжения, подаваемый в соответствующую числовую шину записи-считывания

5. На остальных выходах дешифратора

9 сохраняется нулевой уровень. На всех выходах второго дешифратора адреса присутствует нулевой уровень, B это же время на выходах блока 11 разрядных формирователей тех разрядов, в которые должна быть записана единица, появляются импульсы напряжения, которые подаются по разрядным шинам

6 на эмиттеры транзисторов 3. Тем са— мым обеспечивается протекание разрядных токов записи, обратных токам считывания для каждого запоминающего элемента 2.

Транзисторы запоминающих элементов выбранного числа при этом работают в инверсном режиме. На выходах усилителей с тех разрядов, в которые должен быть записан нуль, сохраняется нулевой уровень напряжения.

Формула изобретения

Зап оминающее устройств о, с одержащее накопитель, выполненный на транзисторах и ферритовых сердечниках, прошитых выходными шинами, подключенными к усилителям считывания, числовыми шинами считывания, одни концы которых соединены с коллекторами соответствующих транзисторов, к эмиттерам которых подключены разрядные шины, а к базам — числовые шины записи-считывания, соединенные с одним из дешифраторов адреса, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, другие концы числовых шин считывания подключены к выходам другого дешифратора адреса.

515151

Изд. Ph

Заказ 6 9

Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская нао., 4

Филиал ППП "Патенр", г. Ужгород, ул. Проектная, 4

Составитель д Рудаков

Редактор Т.Иванова Техред Н.Ханеева Корректор

И.Позняковская