Оперативное запоминающее устройство с обращением к множеству ячеек памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ (11) щ рв

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 07. 10. 74 (21) 2065157/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.05.76.Бюллетень № 19 (45) Дата опубликования описания (51) М. Кл. Q 11С 11/00

Гасударственный комитет

Совете Министров СССР аа делам нзооретений н открытий (53) УДК 681.327.6 (088.8) (72) Авторы изобретения

А. Х. Ганитулин и Г. A. Поляков (71) Заявитель у с (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО С ОБРАЩЕНИЕМ

К МНОЖЕСТВУ ЯЧЕЕК ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно оперативное запоминающее уст» ройство с одновременным обращением к множеству ячеек памяти, содержащее нако- 5 питель, входы которого подключены к блоку записи-регенерации и адресному блоку, а выход - к блоку усилителей считывания, регистры чисел, входы которых соединены через элементы И с выходами блока усили- 10 телей считывания, регистры маски, выходы которых подключены к входам блоков формирования масок.

Недостатком известного устройства является невысокая скорость работы. 15

Йля увеличения быстродействия устройство содержит элементы ИЛИ, дополнительные элементы И, дополнительные регистр маски и регистры чисел, входы которых подключены соответственно к выходам одних дополнительных элементов И и к выходам одного из блоков формирования маски, а выходы через последовательно соединенные другие дополнительные элементы И и элементы ИЛИк входам блока записи-регенерации.

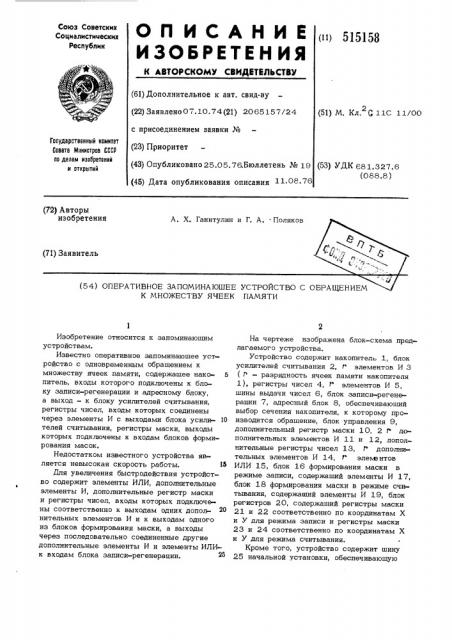

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит накопител 1, блок усилителей считывания 2, Г элементов И 3 (т — разрядность ячеек памяти накопителя

1), регистры чисел 4, 1 элементов И 5, шины выдачи чисел 6, блок записи-регенерации 7, адресный блок 8, обеспечивающий выбор сечения накопителя, к которому производится обращение, блок управления 9, дополнительный регистр маски 10, 2 т= дополнительных элементов И 11 и 12, дополнительные регистры чисел 13, Р дополнительных элементов И 14, т элема нтов

ИЛИ 15, блок 16 формирования маски в режиме записи, содержащий элементы И 17, блок 18 формирования маски в режиме считывания, содержащий элементы И 19, блок регистров 20, содержащий регистры маски

21 и 22 соответственно по координатам Х и У для режима записи и регистры маски

23 и 24 соответственно по координатам Х и У для режима считывания.

Кроме того, устройство содержит шину

25 начальной установки, обеспечиваюшую вь дачу сrrr .ràла 0 установки регистров о устройства в нулевое исходное состояние, шину адреса 26 для выдачи сигнала ( па приема адресов, шину считывания 27, обесгечивающчо выдачу сигнала Q начала ф формирования координатных токов, шину стробнрэвання 28 для выдачи сигнала (строс бпровання, шину запрета 29, обеспечиваю- д шую выдачу сигнала Q начала формироз ванпя токов запрета, шину передачи 30 для выдачи сигнала Q, разрешаюшего вч передачу множества считанных из накопи- 15 теля 1 чисел в арифметическое устройство (rrà чертеже не показано). шину числа

31, эбосгечиваюшуто выдачу сигнала пч разрепаюше, э прием мпэжества чисел из арифметичческого устройства в дополнитель20 ные регистрь.: чис 1 устройства, г шин приема 32 чисел пз арифметического устр:ýr(eò. „=

Рог: стр l0 состоит и триггеров 33.

:. ëäь; регистра маски 10 и дополнительных регистров чпсел 13 подключены соответственно к выходам дополнительных элементов

И 12 и к выходам блэка 16 формирования маски в режиме записи, а выходы через 30 последовате-.ьное соединенные дополнительные элементы И 11, 14 и элементы ИЛИ

15 — к входам блока записи-регенерации 7.

У ,. стройс-.вэ работает следуюшим образом.

При пэстуглспии из устройства управле35 и я ЦВ, 4 li блэк управления 9 сигнала "Обращение эосспечивается следующая последовательность работы блоков устройств, Пэ сигналу Q (шина 25 ) эсушествля— о ется гашение предшествуюшей информации в регистрах 4, 10, 13, 21-24 и в регистрах адресов адресного блока 8, По сигналу g (шина 26) в регистры па адресов по координатам Х и У адресного блока 8 производится прием адресов А и х

А сечения, в регистры 21, 22 — прием коу дэв маски по координатам Х и У в режиме записи, в регистры 23, 24 — прием кодов маски по координатам Х и У в режиме считывания.

При появлении на шине 27 блока управления 9 сигнала g адресным блоком 8 ф выполняется считывание содержимого всех 55 ячеек соответствующего сечения накопителя 1. К этому моменту времени оказывается сформированным с помощью блоков 16 и 18 маски режимов записи и считывания соответственно. Разряды маски в режиме 60 записи формируются блоком 16 так, что в (-ный триггер 33 регистра маски 10 заносится единица, если в L -ую ячейку выбранного сечения надлежит записать число, поступаюшее по входным шинам 32 в регистр 13, L -ый триггер 33 регистра 10 остается в нулевом состоянии, если в L -ю ячейку выбранного сечения надлежит записать информацию с -го регистра числа 4, т. е. регенерировать считанную ранее информацию.

Разряды маски в режиме записи оказываются записанными в соответствуюшие триггеры 33 регистра маски 10, Триггеры 33 регистра 10, содержашие единичные разряды маски, подготавливают к работе сэответствуюшие элементы И 14. Триггеры 33 регистра 10, содержашие нулевые разряды маски, подготавливают к работе соответствуюшие элементы И 11, Одновременно со считыванием информации из накопителя 1 сигналом g, снимаемым с шины 31, разпч решается прием в дополнительные регистры

13 множества чисел, подлежаших записи в накопитель.

Одновременно со считыванием информации из накопителя 1 и ее приемом в соответствуюшие регистры чисел 4 осушествляется прием в дополнительные регистры 13 множества чисел, подлежаших записи.

При появлении на выходной шине 29 сигнал (4,поступаюшего в блок записи-регез нерации 7, а также на каждый элемент И

11 и 14, осуществляется обычным способом запись в соответствующие ячейки выбранного сечения множества чисел, принятых из арифметического устройства, подлежаших записи в накопитель 1 и находяшихся в соответствующих дополнительных регистрах чисел 13 с одной стороны, и регенерация содержимого тех ячеек выбранного сечения, содержимое которых при считывании было занесено в соответствующие регистры чисел 4. Выдача считанных из накопителя 1 чисел производится через элементы И 5 по управляюшему сигналу Q вч формируемому на выходной шине 30 одновременно с сигналом Q . Подготовка к з работе соответствующих элементов И 5 осушествляется с помошью выходных сигналов блока 18 формирования маски в режиме с ч итыван ия.

Формула изобретения

Оперативное запоминающее устройство с обращением к множеству ячеек памяти, содержащее накопитель, входы которого

515158

Составитель В. Рудаков

Редактор Т. Иванова Техред Т, Курилко Корректор Е. Рожкова

ЦНИИПИ 3azas553$.Изд М gg Тир К 723 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 подключены к блоку записи-регенерации и адресному блоку, а выход — к блоку усилителей считывания, регистры чисел, входы которых соединены через элементы И с выходами блока усилителей считывания, регистры маски, выходы которых подключены к входам блоков формирования масок, отличаюшееся тем,что, с целью увеличения быстродействия, оно содержит элементы ИЛИ, дополнительные элементы И, дополнительные регистр маски и регистры чисел, входы которых подключены соответственно к выходам одних дополнительных элементов И и к выходам одного из блоков формирования масок, а выходы через последовательно соединенные другие дополнительные элементы И и элементы .ИЛИ - к входам блока записи-регенерации.