Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ ()бща

ИЗОБРЕТЕН ИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свнд-ву (22) Заявлено 27.02.75 (21) 2108846/24 с присоединением заявки № (23) Приоритет (51) М. Кл. С 11С 17/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (43) Опубликовано 25.05.76Бюллетень №19 (53) УДК 628.327.6 (088.8) (45) Дата опубликования описания 11.08.76 (72) Автор изобретения

А. М. Селигей (7т) Заявитель Киевский завод электРонных вычислительных и УпРавлЯющих машин (54) ПОСТОЯННОЕ ЗАПОИИНА ЮЩЕЕ УСТРОЙСТВО эмиттеров соответствующего многоэмиттерного транзистора 7 и с выходом адресного дешифратора 6.

Устройство работает следующим образом.

Изобретение относится к автоматике и вычислительной технике, в частности к постоянным запоминаюшим устройствам.

Известны постоянные запоминающие устройства, содержашие адресные дешифраторы, адресные токовые шины и элементы выборки.

Однако в таких устройствах содержится большое количество координатных трансформаторов и разделительных диодов, что ус- щ ложняет конструкцию, увеличивает трудоемкость изготовления устройства и снижает его быстродействие и надежность работы.

Цель изобретения — повышение надежности и быстродействия устройства, 15

Для этого в предлагаемом устройстве элементы выборки выполнены в виде многоэмиттерных транзисторов, базы и коллекторы которых соединены с выходами адресных дешифраторов, а каждая из адресных,ЕQ токовых шин соединена с одним из эмиттеров соответствующего многоэмиттерного транзистора.

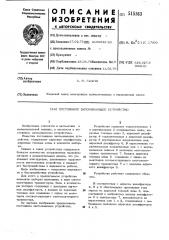

На чертеже изображено предлагаемое постоянное запоминающее устройство. 25

Устройство содержит горизонтальные 1 и вертикальные 2 координатные шины, адресные токовые шины 3, адресный дешифратор 4 горизонтальных и адресный дешифратор 5 вертикальных координатных шин, адресный дешифратор 6, В пересечениях горизонтальных координатных шин 1 с вертикальными шинами 2 включены многоэмиттерные транзисторы 7. Каждая адресная токовая шина 3 соединена с одним из

В соответствии с адресом дешифраторы

4, 5 и 6 обеспечивают протекание тока опроса по адресной токовой шине 3, подключенной к выбранному выходу дешифратора 6 и транзистору 7, находящемуся на пересечении шин 1 и 2, соединенных с выбранными выходами адресных дешифраторов

4и5.

515163

Тираж 72+

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Формула изобретения

Постоянное запо инаюц;ее устройство соцержашеc адресные дешифраторы, адреснь:е токовыо шины и элементы выборки, отлпчаюшееся тем,что,с целью:овьп:ения надежности и быстродей1Л1ИИ iii Заказ 5538 Изд. J4 ф ствия устройства, в нем элементы выбор—

Кр выполнены в виде многоэмиттерных транзисторов, базы и коллекторы которых соединены с выходами адресных дешифраторов, а каждая из адресных токовых шин соединена с одним из эмиттеров соответствующего многоэмиттерного транзистора,