Преобразователь импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К дВтОРСКОМЮ СВИДЕТЕЛЬСТВ

Союз Советских

Социалистических

Республик (") 515268 (61) Дополнительное к авт. свид-ву(22) Заявлено 03.01.75 (21) 2092829/24 с присоединением заявки №(23) Приоритет. (43) Опубликовано 25.05.76.Бюллетень № 19 (45) Дата опубликования описания 30.08.76

Гасударственный комитет

Совета Министроа СССР по делам изооретений и открытий (72) Авторы изобретения

С. В. Куликов и К. А. Чуков (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ИМПУЛЬСОВ ватель дополнительно введены блок преобразования длительности импульсов в напряжение, схема сравнения и триггер, нулевой вход которого соединен со вторым входом преобразователя, единичный вход — с выхоцом схемы сравнения, а прямой выходс нулевым входом первого триггера и выходом преобразователя, инверсный выход дополнительного триггера соединен с перу вым вхоцом преобразователя длительности импульсов в напряжение, второй вхоц которого соединен с инверсным выходом второго триггера, а выхоц — с первым входом схемы сравнения, второй вхоц которой со15 единен с шиной нулевого потенциала.

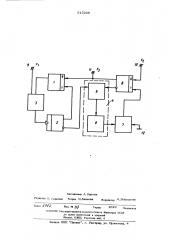

На чертеже изображена блок-схема предлагаемого преобразователя.

Преобразователь состоит из триггеров

gO 1 и, элемента И 3, блока 4 преобразования длительности импульсов в напряжение, выполненного на источнике 5 постоянного по величине заряцно-разрядного тока в интеграторе 6, схемы сравнения 7 и триггера 8.

Изобретение относится к измерительной и вычислительной технике и предназначено для преобразования двух последовательностей импульсов в третью. При этом частота и длительность импульсов третьей последовательности равны соответственно частоте одной и временному интервалу между импульсами другой преобразуемой пэследовательности импульсов.

Известны преобразователи импульсов, соцержыпие триггеры и элемент И, первый вход которого соединен с первой входной клеммой преобразователя, второй входс выходом первого триггера, а выход — со счетным входом второго триггера, прямой выход которого соединен с единичным входом первого триггера.

Нецостатком известных преобразователей импульсов является невысокая точность преобразования, обусловленная неравномерностью частоты преобразованной последовательности импульсов.

Цель изобретения — повышение точности преобразования.

Для этого в предлагаемый преобразо(5!) N. Ka Н ОЗК 5/136 (53) УД1(681.333(088.8) 51 г 26Р, 30

Преобразователь импульсов, содержаший триггеры и элементы И, первый вход которо-, го соединен с первой входной клеммой преобразователя, второй вход — с выхоцом

35 первого триггера, а выход - со счетным вхоцом второго триггера, прямой выход которого соединен с единичным входом первого триггера, о т л и ч а ю ш и и с я тем, что, с целью повышения точности пре40 образования, дополнительно введены блок преобразования .длительности импульсов в напряжение, схема сравнения и триггер, нулевой вход которого соединен со

45 вторым входом преобразователя ециничЭ ный вход - с выхоцом схемы сравнения, а прямой выход — с нулевым вхоцом первого триггера и выходом преобразователя, инверсный выход дополнительного

50 триггера соединен с первым входом преобразователя длительности импульсов в напряжение, второй вход которого соединен с инверсным выходом второго триггера, а выход — с первым входом схемы сравнения, второй вхоц которой соединен с шиной нулевого потенциала, Преобразователь раб-гает слецукшим образом.

Первая последовательность илгпульсов

Г, подается «а первую входную клемму 5 преобразователя, соединенную с оцним из входов элемента И 3, на другой ахоп которого поступаю". импульсы с выхоца триггера 1. Вторая последовательность импульсов F, подается на вторую входную клемму 10 преобразователя, со10 ециненную с одним из вхоцов триггера 8, С выхоца элемента И 3 импульсы подаются на счетный вход триггера 2, на выхоце которого вырабатывается последовательность

15 импульсов, поступающая на один из входов блока 4.

Перед началом работы триггеры 1, 2, 8

t находятся в состояниях, показанных на чертеже.

В момент прихода импульса второй последовательности / F происходит опрокицывание триггера 8, который выключает в источнике 5 цепь разряца интегратора 6.

В момент перехода напряжения интеграто- 25 ра 6 через нуль на выходе схемы сравнения 7 появляется сигнал, перебрасываюший триггер 8 в исходное состояние. При этом выключается цепь разряца интегратора 6 и опрокидывается первый триггер 1, подготавливая элемент И 3 к приему ближайшего импульса из импульсной после— довательности. У

В момент прихода этого импульса опрокидывается второй триггер 2 и вкльснает в источнике 5 цепь заряца интегратора 6.

Зарядный ток поступает на интегратор 6 ,цо момента прихода следующего импульса из импульсной последовательности Г1у после чего второй триггер 2 опрокидывается, выключая в источнике. 5 цепь заряда интегратора 6 и перебрасывая первый триггер 1, который запирает элемент

И 3. На интегра эре запоминается напряжение, пропорциональное временному интервалу между двумя импульсами импульсной последовательности 1 . Iln npuа ходу на третий триггер 8 очередного им- . пульса из импульсной последовательности

F2 производится списывание запомненного на интеграторе 6 напряжения током разряца источника 5 и "процесс заряц интегратора — запоминание -списывание повторяется.

I1а иь хоцной клемме 11 преобразователя об1 азуется послецовательность импульсов Г,. с длительностью, соответствук шей временному интервалу между ил»пульсами импульсной последовательности

F и с частотой, соответствующей частоте импульсов импульсной послецовательности Г,, H установившемся режиме происходит компенсация погрешностей, вызванных разбросом порога срабатывания схемы сравнения 7, второй вхоц которой соединен с шиной нулевого потенциале 12, и запазцыванием, вносимым конечным временем переключения логических элементов, а также изменениями постоянной интегратора 6.

Кроме того, исключается погрешность, вносимая разбросом параметров источника постоянного по величине заряцно-разряцного тока, так как заряц и разряд интегратора осуществляют оцним и тем же по величине гоком, что еше более увеличивает точность преобразования.

Формула изобретения

515268

Заказ ХЕРР

Иэд. М //P Тнращ

ШГИИПИ Государственного комитета Совета Министров СССР

„.по делам изобретений и открытий

Москва, ll3035, Раушская наб., 4

Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель А. Наумов кто р Г (IDaHoaa Texpen H.Xaaeeaa Kpppeqqpp >. « ермаки