Быстродействующий компаратор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик (11) 515272 (61) Дополнительное к авт. свид-ву(22) Заявлено 22.11.73 (21) 1971 956/21 с присоединением заявки №вЂ” (23) Приоритет

2 (51) М. Кл. Н ОЗК 5/20

05В 1/01 роударстоеинмй комитет

Совета Миниотроо СССР но делам изобретений н открытий (43) Опубликовано 25.05.76.Бюллетень №1 g (53) УДК621.374.335 (088.8) (45) Дата опубликования описания 30. 08 76 (72) АвтоР Е. A. Коломбет, А. А. Лебедев, Л. А. Михеев, Я. Я. Акментыньш изобретения и А. Г. Апексеенко (71) Заявитель (54) БЫСТРОДЕЙСТВУЮШИЙ КОМПАРАТОР

Изобретение относится к импульсной технике и может использоваться в аналоговых вычислительных машинах, системах управления и радиоизмерительной аппаратуре.

Один из известных компараторов содержит дифференциальные усилители (ДУ), стабилизированный источник постоянного тока (СИПТ) и триггер-зашелку (11 . Однако этот компаратор имеет не,цостаточное быстродействие, потому что его транзисторы рабо-10 тают в режиме насышения.

Наиболее близким к изобретению техническим решением является быстродействуюший компаратор, содержаший два ДУ и

СИПТ f 2) . 15

Недостаточные быстродействие и чувствительность этого компаратсра обьясняют ся последовательной обработкой входной информации в каждом ДУ, низким входным сопротивлением, требующим больших вхо шых 20 токов для получения высокого быстродействия.

Целью изобретения является повышение быстродействия и чувствительности компаратОра. 25

Для этого входной дифференциальный каскац выполнен на двух,цвухэмиттерных транзисторах, первые эмиттеры которых объединены и образуют первый ДУ, вторые эмиттеры двухэмиттерных транзисторов поцклкяены к каскацу ускорения, выполненному на трех транзисторах с объединенными эмиттерами и подключенному к СИПТ, причем первые эмиттеры двухэмиттерных транзисторов соединены с коллектором оцного из транзисторов каскаца ускорения, база которого подключена к второму эмиттеру первого двухэмиттерного транзистора, а втОрОЙ эмиттер второго двухэмиттернОгО транзистора подключен к обьединенным базам двух других транзисторов каскада ускорения, один из коллекторов которых поцклкяен K первым эмиттерам двухэмит терных транзисторов, а другой из коллекто» ров подключен к эмиттерам второго ДУ.

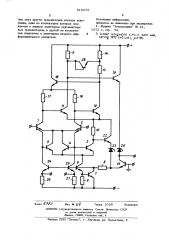

На чертеже приведена принципиальная электрическая схема компаратора.

Быстродействуюший компаратор содержит входной дифференциальный каскад на двухэмиттерных транзисторах 1 и 2, первые

515272 эмиттеры которых обье,цинены и образуют первый ДУ, а вторые эмиттеры подключены к входам каскада ускорения, на транзисторах 3-5 с обьединенными эмиттерами, подключенными к выходу первого 5

СИПТ, построенного на транзисторах

6 и 7 и резисторах 8, 9, причем второй эмиттер транзистора 1 поцключен к базе транзистора 5, коллектор которого подключен к обьединенным эмиттерам транзисто- 10 ров 1 и 2, а второй эмиттер транзистора

2 подключен к обьециненным базам транзисторов 3 и 4. Коллектор транзистора 4 подключен к обьециненным эмиттерам тран« зисторов 1 и 2, а коллектор транзистора 15

3 через резистор 10 подключен к обьециненным эмиттерам транзисторов 11 и 12,образующих второй ДУ. В коллекторных цепях транзисторов 11 и 12 соответст» венно включены нагруэочные резисторы 20

13, 14 и 15, а в цепях коллекторов транзисторов 1 и 2 — резисторы 16 и 17.

Коллекторы транзисторов 1 и 2подключены к базам соответственно транзисторов 11 и 12 и образуют второй дифференциальный усили- 25 тельный каскад, причем коллектор транзи стора 12 подключен к базе транзистора

18, коллектор которого соединен с положительной шиной питания, а эмиттер - с резисторами 16 и 17. Коллектор транзи- ® стора 11 подключен к базе транзистора 19, коллектор которого соединен с положительной шиной питания, е эмиттер-через стабилитрон 20 с коллектором транзистора 2 1, база которого заземлена, а эмиттер соединен с резистором 8. Эмиттеры транзисторов

11 и 12 соединены с коллектором транзистора 22, база которого подключена к коллектору транзистора 3, а эмиттер— через стабилитрон 23 к эмиттеру транзи40 стора 21, К базам транзисторов 4 и 5 подключены коллекторные выхоцы второго и третьего управляемых СИПТ на транзисторах 24 и 25, базы которых объединены и подключены к базе транзистора 6, а эмиттеры через резисторы 26 и 27 соединены с отрицательной шиной питания.

Межцу резисторами 13 и 15 включен диод 28.

При подаче на базы транзисторов

1 и 2 равных напряжений на выхоце устройства — коллекторе транзистора 21— устанавливается выходное напряжение, превышающее порог срабатывания подключенной к нему логической схемы.

Поступление на входы транзисторов

1 и 2 .цифференциального сигнала приводит к оцнозначному переходу выхоцного напряжения в уровни, соответствующие логическому "О или "1

Ток в первом ДУ равен сумме коллекторных токов транзисторов 4 и 5, так как токи через транзисторы 24 и 25 сравнительно малы. Ток во втором ДУ равен сумме коллекторных токов транзисторов 3 и 22. Причем сумма коллекторных токов транзисторов 3-5 постоянна и определяется током транзистора 6. Все транзисторы компаратора работают в активном режиме.

При подаче отрицательного сигнала на базу транзистора 1 при заземленной базе транзистора 2 напряжение на входе второго

ДУ в первый момент достигает большой величины и на выходе компаратора устанавливается "О . Транзистор 11 начинает насыщаться, оцнако практически одновременно начинает запираться транзистор 5, что приводит к уменьшению тока через первый

ДУ, стремящегося к величине коллекторного тока транзистора 4. Из-за уменьшения тока в первом ДУ уменьшается дифференциальный сигнал на его выходе, а след вательно, и степень насыщения транзистора 11. Благодаря этому в канале усиления компаратора отсутствуют транзисторы в режиме глубокого насыщения при подаче отрицательного сигнала на вход и,цлительность переходного процесса иэ одного логического состояния в другое ограничивается только временем перезаряца паразит» ных емкостей и на практике не превышает

20 нсек.

Формула изобретения

Быстродействующий компаратор, содержащий два дифференциальных усилителя и стабилизированный источник постоянного тока, отличающийсятем,что, с целью повышения быстродействия и чувст вительности, входной дифференциальный каскад выполнен на,цвух двухэмиттерных транзисторах, первые эмиттеры которых обьединены и образуют первый дифференциальный усилитель, вторые эмиттеры двухэмиттерных транзисторов подключены к каскаду ускорения, выполненному на трех транзисторах с обьединенными эмиттерами и подключенному к стабилизированному источнику постоянного тока, причем первые эмиттеры двухэмиттерных транзисторов соединены с коллектором оцного из транзисторов каскаца ускорения, база которого подключена ко второму эмиттеру первого двухэмиттерного транзистора, а второй эмиттер второго двухэмиттерного транзистора подключен к обьециненным ба515272

Заказ 5 РР2

Изд. 1Ф //

ЦНИИПИ Государственного комитета Совета Министров СССР по. делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 зам двух других транзисторов каскада ускорения, один из коллекторов которых поцключен к первым эмиттерам,цвухэмиттерных транзисторов, а другой из коллект . ров подключен к эмиттерам второго дифференциального усилителя.

Источники информации, принятые во внимание при экспертизе.

1. Журнал Электроника Хз 21, 1972 r, стр. 56.

5 2 ° ьиеаг tategrAted, circ it ать Ьоо, аргтц 1972 {NG 003), 1цд710.

Тираж 1029 Подписное