Устройство для сопряжения вычислительной машины с каналами связи

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 51603I

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 14.12.73 (21) 1978502/18-24 с присоединением заявки i¹ (23) Приоритет

Опубликовано 30.05.76. Бюллетень ¹ 20

Дата опубликования описания 22.06.76 (51) М Кл г G 06F 3/00

Государственный ком итет

Совета Министров СССР (53) УДК 684.14(088 8) по делам изобретений

1 и открытий (72) Авторы изобретения

Г. В. Абрамов, В. Е. Евстигнеев и О. М. Невс (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ

Изобретение относится к области связи и может быть применено в технике передачи и приема в последовательном коде информации от вычислительных машин, работающих в параллельном коде.

Известно устройство для сопряжения вычислительной машины (ВМ) с каналами связи, содержащее преобразователь кода, блок коммутации, первые вход и выход которого подключены соответственно к первым входу и выходу устройства, а вторые вход и выход— соответственно к первым выходу и входу преобразователя кода, блок управления коммутацией, выход которого соединен с третьим входом блока коммутации, блок буферной памяти, первые вход и выход которого подключены соответственно к вторым выходу и входу устройства, а вторые вход и выход — соответственно к вторым выходу и входу преобразователя кода.

Для обращения ВМ к известному устройстству сопряжения осуществляется прерывание выполнения программ ВМ, при этом в канал связи передается т бит информации. При передаче т.п бит информации в один канал связи необходимо провести и обращений к известному устройству сопряжения, что связано с большими потерями времени.

Цель изобретения — увеличение быстродействия устройства.

Это достигается тем, что в известное устройство введены узел формирования, группа элементов «И», регистры управления, узел поиска левой единицы, узел распределения управляющих сигналов, элемент «И», первый и второй триггеры. Выходы группы элементов «И» соединены с первыми входами блока управления коммутацией, первые входы регистров управления подключены к третьему входу уст10 ройства, вторые входы — к выходам узла формирования, а выходы связаны с информационными входами группы элементов «И».

Входы узла поиска левой единицы подсоединены к выходам регистра управления, а

15 выходы — к первому входу узла формирования и к управляющим входам группы элементов «И». Первый вход узла распределения управляющих сигналов подключен к выходу узла поиска левой единицы, выход — к третье20 му входу блока буферной памяти. Вход первого триггера соединен с третьим входом устройства, а выход — с вторыми входами блока управления коммутацией и узла распределения управляющих сигналов. Первый вход

25 элемента «И» подключен к четвертому входу устройства, а выход — к второму входу узла формирования и третьему входу преобразователя кодов. Входы установки в единицу и нуль второго триггера связаны соответствен30 но с пятым входом устройства и первым вы516031

65 ходом узла формирования, а единичный и нулевой выходы — соответственно с вторым входом элемента «И» и третьим выходом устройства.

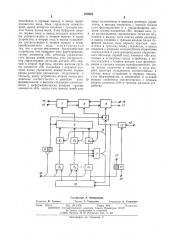

Блок-схема предлагаемого устройства для сопряжения вычислительной машины с каналами связи приведена на чертеже, где 1— блок коммутации; 2 — преобразователь кода;

3 — блок буферной памяти; 4 — блок управления коммутацией; 5ь 5, ..., 5 — регистры управления; бь 6, ..., 6 — группа элементов «И»; 7 — узел поиска левой единицы; 8— узел распределения управляющих сигналов;

9 — первый триггер; 10 — узел формирования;

11 — второй триггер; 12 — элемент «И»; 13— выходная цепь узла 7 поиска левой единицы;

14 — выходная цепь устройства, подключенная к передающим каналам связи; 15 — входная цепь устройства, подсоединенная к приемным каналам связи; 16 — входная цепь устройства, соединенная с выходными шинами

ВМ; 17 — выходная цепь устройства, подключенная к входным шинам ВМ; 18 — входная цепь устройства, связанная с выходными кодовыми шинами ВМ; 19 — входная цепь устройства, подключенная к генератору тактовых импульсов; 20 — входная цепь устройства, подсоединенная к «пусковой» шине ВМ; 21— выходная цепь «Готовность» устройства, подключенная к входу ВМ.

Устройство работает следующим образом.

В случае отсутствия информации (нулевых кодах) на регистрах 5ь 5, ..., 5 блок 1 коммутации отключает каналы связи от преобразователя 2 кодов. Триггер 11 блокирует прохождение тактовых сигналов через элемент

«И» 12. По цепи 21 в ВМ поступает сигнал

«Готовность».

Рассмотрим работу устройства при записи на регистры 5ь 5, ..., 5 соответственно кодов

100 ... 0; 010 ... 0; ...; 00... 1

После записи информации о режиме обмена по цепям 18 на регистры 5ь 5, ..., 5 и на триггер 9 в цепи из ВМ поступает сигнал

«Пуск», по которому триггер 11 переключается в положение, разрешающее прохождение тактовых импульсов через элемент «И» 12.

Узел 7 осуществляет поиск крайней левой единицы кодов регистров 5ь 5, ..., 5, формирует в цепи 13 управляющий сигнал, подключая регистр 5i через элементы 6> к входу блока 4. Тем самым первый канал связи подсоединяется к выходу преобразователя 2.

Одновременно узел 8 формирует сигнал на подключение первого регистра блока 3 к входу преобразователя 2. При подаче тактовых импульсов преобразователь 2 преобразует параллельный код регистра блока 3 в последовательный код, поступающий по цепи 14 в первый канал связи.

По окончании преобразования первых т бит сообщения в последовательный код узел

10 формирует сигнал обнуления регистра 5ь

После этого узел 7 формирует новый управляющий сигнал, подключая регистр 5 (на ко5

55 тором записан код 01 ... О) через элементы 6> к входу блока 4, тем самым к выходу преобразователя 2 подсоединяется второй канал связи.

Одновременно узел 8 формирует сигнал на подключение к входу преобразователя 2 второго регистра блока 3.

При поступлении тактовых импульсов преобразователь 2 преобразует параллельный код регистра блока 3 в последовательный код. По окончании преобразования вторых т бит сообщения узел 10 формирует сигнал обнуления регистра 5>. В дальнейшем работа устройства происходит аналогично до тех

IIop, пока необнулены все регистры, кроме 5 .

После преобразования последнего сообщения узел 10 формирует сигнал на обнуление регистра 5„и на переключение триггера 11. Нра этом по цепи 21 в ВМ поступает сигнал «Готовность», а устройство готово для проведения следующего сеанса связи.

В рассмотренном режиме за одно обращение,к устройству переда на информация для всех каналов связи.

При записи на регистры 5ь 5, ..., 5„соответственно кодов 10 ... С; 10 ... 0; 10 ... 0 ðàáîтает устройство таким образом, что все регистры блока 3, начиная с первого, последовательно подключаются к первому каналу связи. При этом другие каналы связи отключены блоком 1 от блока 3, а в первый канал связи передано т и бит информации.

В случае записи на регистры 5;, 5, ..., 5 соответственно кодов 10 ... 0; 10 ... 0; 0 ... 01 устройство сопряжения подсоединяет последовательно первые два регистра блока 3 к первому каналу связи, а последний регистр блока 3 — к последнему и-му каналу связи.

Работа устройства в режиме «Прием» отличается от режима «Передача» состоянием триггера 9, подключением блоком 1 приемных каналов связи, подсоединенных к цепи

15, и обратным преобразованием (последовательного кода из каналов связи в параллель ый код), осуществляемым преобразователем 2. По окончании приема информации из каналов связи в блок 3 в цепи 21 так же, как и в рассмотрен ом режиме, формируется сигнал «Готовнос1ь».

Так как за одно обращение к устройству по программе ВМ vñåãëa передается максималь ый объем т.п бит информации, распределяющийся по отдельпым каналам связи в соответствии с кодами па регистрах 5ь 5, 5, то время, затрачиваемое ВМ на организацию сопряжения с каналами связи, минимально.

Формула изобретения

Устройство для сопряжения вычислительной машины с каналами связи, содержащее преобразователь кода, блок коммутации, первые вход и выход которого подключены соответственно к первым входу и выходу устройства, а вторые вход и выход подключены соот516031

Составитель А, Амбарцумян

Редактор И. Грузова Техред 3. Тараненко Корректор А. Степанова

Заказ 1351/3 Изд. Ме 1376 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-З5, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ветственно к первым выходу и входу преооразователя кода, блок управления коммутацией, выход которого соединен с третьим входом блока коммутации, блок буферной памяти, первые вход и выход которого подключены соответственно к вторым выходу и входу устройства, а вторые вход и выход подключены соответственно к вторым выходу и входу преобразователя кода, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства, оно содержит узел формирования, группу элементов «И», регистры управления, узел поиска левой единицы, узел распределения управляющих сигналов, элемент «И», первый и второй триггеры, причем выходы группы элементов «И» соединены с первыми входами блока управления коммутацией, первые входы регистров управления подключены к третьему входу устройства, вторые входы подключены соответственно к выходам узла формирования, а выходы соединены соответственно с информационными входами группы элементов «И», входы узла поиска левой единицы подключены к выходам регистра управления, а выходы соединены с первым входом узла формирования и с управляющими входами группы элементов «И», первый вход уз5 ла распределения управляющих сигналов подключен к выходу узла поиска левой единицы, а выход соединен с третьим входом блока буферной памяти, вход первого триггера подключен к третьему входу устройства, а выход

10 соединен с вторыми входамиблока управления коммутацией и узла распределения управляющих сигналов, первый вход элемента «И» подключен к четвертому входу устройства, а выход соединен с вторым входом узла формиро15 вания и третьим входом преобразователя кода, входы установки в единицу и нуль второго триггера подключены соответственно к пятому входу устройства и первому выходу узла формирования, а единичный и нулевой

20 выходы соединены соответственно с вторым входом элемента «И» и третьим выходом устройства,