Формирователь суммы на мдп-транзисторах

Иллюстрации

Показать всеРеферат

О П И С А Н- И Е

ИЗОБРЕТЕН ИЯ (iiI 5I 6038

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 22.12.72 (21) 1866516!24 (51) Л1. Кл.- 6 06Г 7 50 с присоединением заявки ¹

Совета Министров СССР ло делам изобретений и открытий (53) УДК 621.374.32 (088.8) Опубликовано 30.05.76. Бюллетень ¹ 20

Дата опубликования описания 06.07.76 (72) Авторы изобретения

Н. А. Кукин и Г. В. Милославский (71) Заявитель (54) ФОРМИРОВАТЕЛЬ СУММЫ НА МДП-ТРАНЗИСТОРАХ

ГосУдарствеиный комитет (23) Приоритет

Устройство относится к вычислительной технике и может быть использовано для построения арифметических устройств в универсальных и специализированных вычислительных машинах.

Известен формирователь суммы на МДПтранзисторах, содержащий две группы логических схем формирования частичны; сумм, в которых четыре транзистора, образующих первую группу, истоками соединены с первой шиной питания, затворами соответственно— с шинами прямого и инверсного значений кодов двух слагаемых, стоками два транзистора этой группы соединены с истоками нагрузочного и проходного транзисторов и со стоками двух пар транзисторов второй группы, другие два транзистора первой группы стоками соединены с истоками двух транзисторов, образующих вторую группу, затворы которых соединены с шинами прямого и инверсного значений кодов третьего числа. Сток первого проходного транзистора подключен к стоку первого ключевого транзистора и к истоку третьего нагрузочного и блокировочного транзисторов, а стоки и затворы всех нагрузочных транзисторов объединены и подключены к второй шине питания.

Известный формирователь суммы содержит большое количество элементов и сложную схему соединений.

Целью изобретен гя является упрощение устройства.

С этой целью формирователь суммы выполнен по двухтактной схеме, в которой второй проходной транзистор соединен с затвором третьего клпочевого транзистора, исток которого соединен с истоками первых двуx ключевых транзисторов н с затворами проходных транзи=торов II подключен к первой шине тактовых импульсов, сток третьего ключевого транзистора соединен со стоком второго ксиочевого транзистора, с затвором первого ключевого транзистора и с истоком четвертого нагрузочного транзистора, а затвор блокпро15 вочного транзистора, стоком подключенный к затвору второго ключевого транзистора, соединен с второй шиной тактовых импульсов.

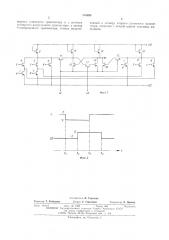

На фиг. 1 показана схема предлагаемого формирователя; на фпг. 2 приведена времсн20 ная диаграмма подачи на формирователь двух последовательностей тактовых импульсов, Формирователь содержит логические транзисторы 1 5 и нагрузочный транзистор 6, 25 реализующие операцию,=ас+ас+в, логические транзисторы 1, 2, 7, 8 и 9. нагрузочный транзистор 10, реализующие операцию

f,=àñ+àñ+â; проходные транзисторы 11 и

30 12; триггер хранения суммы, образованный

516338

30 первым и вторым ключевыми транзисторами

13 и 14, нагрузочным1! транзисторами 15, 16 и блокировочным транзи тором 17, и третий ключевой транзистор 18. Причем ключевой транзистор 18 одновременно с ключевым транзистором 14 триггера хранения суммы выполняет операцию получения значения суммы S=fl+f .

Проходной транзистор 11 соединяет выход логической схемы, реализующей операцию

) 1, с нулевым плечом триггера суммы (сток первого ключсвого транзистора), а проходной транзистор 12 — выход логической схемы, рсализукнцсй операцию t,, с затвором треп.его ключевого транзистора 18, исток которого полкл!Очсн к истокы BTUpol I(, 110HBBol 1 1эс1нз!1стОр а, а! с l ок к с! Ок BTopol О к 110HBBol o TpBHзистора. Затворы проходных транзисторов, истоки всех ключевых транзисторов подключены к шине первой последовательности тактовых импульсов 19, а затвор блокировочного транзистора 17 — к второй последовательности тактовых импульсов 20. Истоки транзи.торов 1 и 2 связаны с первой шиной питания 21, а нагрузочные транзисторы 6, 10, 15 и 16 затворами и стоками подключены к второй шине питания 22.

В режиме хранения информации (до момента времени t, (фиг. 2) . Высокий уровень напряжения по шине 19 поддерживает в закрытом состоянии проходные транзисторы 11 и 12 и в открытом состоянии — ключевые транзисторы 13, 14 и 18. Блокировочный транзистор 17 в это время открыт по затвору отрицательным уровнем напряжения по шине

".,О. Благодаря этому триггер суммы способен ранить информацию при условии подачи по-.тоянного напряжения — E по шине 22 отно< ительно шины 21. Динамический режим сложения входных величин а, в и с в схеме ооеспечивается при подача сдвинутых друг относительно друга двух последовательностей тактoBhlx импульсов (см.,фиг. 2).

При поступлении отрицательного импульса по шине 19 открываются по затворам проходные транзисторы 11 и 12 и закрываются по истокам ключевыа транзисторы 13, 14 и 18.

В этот момент времени (1! — t2 на фиг. 2) происходит сложение входных величин а, в и г и запоминание величин fl u f2 на емкости затвор — подложка транзистор 14 и 18.

Вследствие того, что транзистор 14 закрыт по истоку, предыдущее значение суммы S, полученное ранее, сохраняется прежним.

Далее, в момент времени tq по шине 20 на схему поступае! положительный перепад напряжения, который закрывает блокировочный транзистор 17. В момент времени t,, когда олокнровочный транзистор переходит в закрытое состояние, оканчивается отрицательный импульс по шине 19. В этот момент времени закрываются проходные транзисторы

11 и 12 и открываются по истоку все ключевые транзисторы. Начиная с момента 1р

5i)

65 благодаря тому, что все ключевые транзисторы триггера и ключевой транзистор 18 открь! ! 1, информация на затворах транзи торов 14 и 18 формирует новое значение S на единичном плече триггера суммы, соответствующее знач ниям а, в и с, поступившим на схему в интервале

t,— t>. Значение S единичного плеча триггера поступает в дальнейшем на затвор ключевого транзистора 13, на стоке которого формируется инверсное значение величины S.

После этого в момент времени /4 оканчивается положительный перепад по шине 20.

Блокировочный транзистор 17 открывается. за мы ка1! по.10?ките;! ьну10 оор атныго св!1 зь в триггере суммы. Начиная с момента времени в схеме вновь обеспечивается режим pàнсния полученной величины S.

В случае использования формирования суммы в сумматоре схема формирования переноса может оыть получена аналогично схеме формирования суммы с помощью логической схемы, реализующей функцию fg — с(а+в) +в, проходного транзистора и триггера хранения переноса, которые с шинами питания 21 и 22 и с шинами тактовых импульсов 19 и 20 соединяются аналогично описанным выше связя м формирователя с м мы.

Предлагаемый формирователь суммы относится к кла.су динамических схем с импульсным режимом записи информации и со статиче. ким рехкимом хранения ее.

Формула изобретения

Формирователь суммы на МДП-транзисторах, содержащий две группы логических схем формирования частичных сумм, в которых четыре транзистора, образующих первую группу, истоками соединены с первой шиной питания, затворами — соответственно с шинами прямого и инверсного значений кодов двух слагаемых, стоками два транзистора этой группы соединены с истоками нагрузочногo и проходного транзисторов и со стоками двух пар транзисторов второй группы, другие два транзистора первой группы стоками соединены с истоками двух транзисторов, образующих вторую грхппу, затворы которых соединены с шинами прямого и инверсного значений кодов третьего числа, причем сток nepBol o проходного транзистора подкгночен к стоку первого ключевого транзистора и к истоку третьего нагрузочного и блокировочного транзи.торов, а стоки и затворы всех нагрузочных транзисторов объединены и подключены к второй шине питания, о т л и ч а ю щ и йся тем, что, с целью упрощения устройства, формирователь выполнен по двухтактной схеме, в которой второй транзистор соединен с затвором третьего ключевого транзистора, исток которого соединен с истоками первых двух ключевых транзисторов и с затворами проходных транзисторов и подключен к первой шине тактовых импульсов, сток третьего ключевого транзистора соединен со стоком второго ключевого транзистора, с затвором

516038 фиг. 3,7 го

Фиг.2

Составитель И. Горелова

Текред 3. Тараненко

Редактор Т, Рыбалова корректор Л. Орлова

Заказ !416/7 Изд. ¹ 1395 Тираж 869 П одп и I I Ol

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, iK-35, Раушская «ао, д. 4/5

Типография, пр. Сапунова, 2 первого ключевого транзистора и с истоком четвертого нагрузочного транзистора, а затвор

1локировочного транзистора, стоком подключенный к затвору второго ключевого транзистора, соединен с второй шиной тактовык импульсов.

Г !

1! !