Комбинированное устройство для вычисления функций

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

И ЗО БРЕТ Е Н И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1ttt 5I6O62

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву (22) Заявлено 29.01.74 (21) 1991729 24 (51), 1. 1,л. - С 063 3, 60 с присоединением заявки М

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (23) Приоритет

Опубликовано 30.05.76. Бюллетень М 20 (53) УДК 681.34 (088.8) Дата опубликования описания 06.07.76 (72) Авторы изобретения

В. П. Боюн и Л. Г. Козлов

Ордена Ленина институт кибернетики АН Украинской ССР (71) Заявитель (54) КОМБИНИРОВАННОЕ УСТРОЙСТВО

ДЛЯ ВЬ!Ч ИСЛЕН ИЯ ФУНКЦИЙ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в управляющих системах и гибридных вычислительных устройствах для вычисления функций в следящем режиме с постоянны vl шагом по аргументу.

Известно комбинированное устройство для вычисления функций, содержащее аналоговый вычислительный блок, подключенный входом через цифро-аналоговый преобразователь к выходу буферного запоминающего блока и соединенный выходом с входом аналого-цифрового преобразователя, выход которого подключен к информационному входу цифрового вычислительного блока, соединенного выходом с информационным входом буферного запоминающего блока.

Недостатком известного устройства является пониженная динамическая точность вычислений, возникающая в замкнутой системе за счет временной задержки информации в цифровом вычислительном блоке.

Цель изобретения — повышение динамической точности.

Это достигается тем, что предлагаемое устройство снабжено логическим элементом

«ИЛИ» и блоком определения знака приращения аргумента, соединенным входом - выходом аналого-цифрового преобразователя и подк.поченным выходами отрицательног0, нулевого It положительного приращений соответственно к первому, второму и третьему управляющим входам буферного запоминающего блока. Выходы отрицательного и положительного приращений соединены также с входами элемента «ИЛИ». подключенного выходом к управляющему входу цифрового вычислительного блока.

Кроме этого, буферный запоминающий блок

10 содержит три регистра, входные и выходные ключи, клочи передачи, элемент «ИЛИ» и линни задержки, причем выходы первого, второго It третьего регистров соединены через выходные кл1очп, 3 правля!Ощпс входы кото15 рых подключены соответственно к первому, второму п третьему управляющим входам буферного запоминающего блока. со входамп элемента «ИЛИ», соединенного выходом с выходом буферного запомпнающсго блока. Входы

20 и выходы первого и третьего регистров соединены соответственно через ключи передачи с выходами и входами второго регистра. Информационный вход буферного запоминающего блока подключен через входные ключи к входам

25 первого и третьего регистров. Первый управ",ÿþùIté вход буферного запоминающего блока соединен с управляющими входами ключей передачи с второго регистра на третий регистр, подключен через первую линию за30 держки к управляющим входам ключей пе516062 редячи с первого ре1Н1стря ня второй регистр и через вторую линию задер>кки — к управляющим входам входных ключей первого регистра, а третий управляющий вход буферного запоминающего блока соединен с управляющими входами ключей передачи с второго регистра па первый регистр, подключен через треть о линию задержки к управляющим входам ключей передачи с третьего реги тра на второй регистр и через четвертую лини1о задержки — к управляющим входам входных ключей третьего регистра.

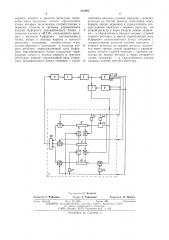

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит аналоговый вычислительный блок 1, выход которого через аналого-цифровой преобразователь 2 подключен к информационному входу цифрового вычислительного блока 3, а вход блока 1 соединен с выходом цифро-аналогового преобразователя

4. Выход преобразователя 2 связан с входом блока 5 определения знака приращения аргумента, выходы отрицательного и положительного приращений блока 5 подключены через логический элемент «ИЛИ» 6 к управляющему входу цифрового вычислительного блока 3 и соединены с первым и третьим управляющим входами буферного запоминающего блока 7, второй управляк1щий вход которого подключен к выходу нулевого приращения блока 5. Выход буферного олокя 7 соединен с входом цифро-аналогового преобразователя 4, а информационный вход подключен к выходу цифрового вычислительного олока 3.

Буферный блок 7 содержит регистры 8, 9, 10, выходные ключи 11, 12, 13, входные ключи 14, 15, ключи передачи 16 — 19, элемент

«ИЛИ» 20 и линии задержки 21 — 24. Выходы регистров 8 — -10 через ключи 11--13, управляющие входы которых соединены с управляющими входами блока 7, подключены к входам элемента «ИЛИ» 20. Входы и выходы регистров 8 и 10 соединены соответственно через ключи 16 — 19 с выходами и входами регистра

9, информационный вход блока 7 ч. р"з кгпочи 14 и 15 — с входами 8 и 10 регистров.

Первый управляющий вход блока 7 соединен с входами ключей 18 и через линии задержки 23 и 24 с входами ключей 19 и 14.

Третий управляющий вход блока 7 связан с входами ключей 16 и через линии задержки

21 и 22 с входами ключей 17 и 15.

Устройство работает следующим образом.

Вначале вычисляют и записывают в регистры 8, 9 и 10 значения функции для значения аргумента с отрицательным приращением

Х 1=Х, — ЛХ, начального значения аргумента Хо и значения аргумента с положительным приращением Х+1=Х<+AХ соответственно. Затем на кождом шаге вычислений блок

5 определяет знак приращения аргумента и вырабатывает сигналы на выходах 25 — 27.

Для отрицательного приращения аргумента соответствующее ему значение функции с реГистра 8 через ключи 11 и элемент «ИЛИ» 20

G0

G5 выдается ня вход цпфро-аналогового прсооразовятсля 4. Одновременно содержимое р"рисгра 9 переписывается через ключи 18 H

Для нулевого приращения аргумента соответствующее ему значение функции с регистра 9 через ключи 12 и элемент «ИЛИ» 20 выдается на вход цифро-аналогового преобразователя 4.

Для положительного приращения аргумента соответствующее ему значение функции с регистра 10 через ключи 13 и элемент «ИЛИ»

20 выдается на вход цифро-аналогового преобразователя 4. Одновременно содержимое регистра 9 через ключи 16 переписывается на регистр 8. Затем через время, определяемое линией задержки 21, содержимое регистра 10 через кл1очи 17 переписывается на регистр

9, после чего через время, определяемое линией задержки 22, через ключи 15 на регистр ! 0 заносится 3IIHчени фуllYIIIIII, вычис.ленное в цифровом вычислительном блоке 3, для 110ложптсльнОГО 11PI IPiIIIIPIIIIЯ Я1)Г мента 1111 сле, 1м1ои1ем п1аге.

Формула изобрстения

1. Комбинированное устройство для вычисления функций, содержащее аналоговый вычисл1ггельный блок, подключенный входом через цифро-аналоговый преобразователь к выходу буферного запоминающего блока и сОсдиненный выходом с входом япс1лого-цифрового преобразователя, выход которого подключен к информяционнОму входу циф1)ОВОГО вычислительного олока, соединенного выходом с информационным входом буферного запоминающего блока, о т л и ч а ю щ е е с я тем, что, с целью повышения динамической точности, в него дополнительно введены логический элемент «ИЛИ» и блок определения знака приращения аргумента, соединенный входом с выходом аналого-цифрового преобразователя и подключенный выходами отрицательного, нулевого и положительного приращений соответственно к первому, второму и третьему управляющим входам буферного запоминающего блока, причем выходы отрицательного и полохкптельного приращений соединены также с входами элемента «ИЛИ», подкл1оченного выходом к управляющему входу цифрового вычислительного блока.

2. Комбинированное устройство по п. 1, о тл и ч à 10 щ е е с я тем, что буферный запоминающий блок содержит три регистра, входные и выходные ключи, ключи передачи, элемент

«ИЛИ» и линии задержки, причем выходы

516062

Составитель С. Казиндв

Техред 3. Тараненко

Корректор Л. Орлова

Редактор Т. Рыбалова

Заказ 1416/!2 Изд. ¹ 1395 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, )I(-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 первого, второго и третьего регистров соединены через выходные ключи, управляющие входы которых подключены соответственно к первому, второму и третьему управляющим входам буферного запоминающего блока, с входами элемента «ИЛИ», соединенного выходом с вь!ходом буферного запоминающего блока, входы и выходы первого и третьего регистров соединены соответственно через ключи передачи с выходами и входами второго регистра, информационный вход буферного запоминающего блока подключен через входные ключи к входам первого и третьего реги. тров, первый управляющий вход буферного запоминающего блока соединен с управЛ5!!Ощимп Входаъ!и кл!Очей передачи с BTQJ)01 0 регистра на третий регистр, подключен через первую линию задержки к управляющим входам ключей передачи с первого регистра на

5 второй регистр и через вторую линию задержки — к управля!ощим входам входных ключей первого регистра, а третий управляющий вход буферного запоминающего блока соединен с управля!ощимп входами ключей передачи с

10 второго регистра на первый регистр, подключен через третью линию задержки к управляющим входам ключей передач с третьего регистра на второй регистр и через четвертую линию задержки — к управляющим входам

15 входных ключей третьего регистра.