Устройство для передачи и приема частотной информации

Иллюстрации

Показать всеРеферат

О П

ИЗОБРЕТЕНИЯ рр 516084 ьовз Советских

Социалистических

Респуояик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву. (22) Зяавлено 21.03.75 (21) 2115605/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.05.76. Бюллетень _#_ 20

Дата опубликования описания 30.11.76 (51) M. Кл.2 б 08С 19/12

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.398(088.8) (72) Авторы изобретения

Ф. А. Катков, А. Б. Попов, А. А. Новацкий, В. С. Чернега, Г. Б. Остапенко и В. В. Костюченко (71) Заявитель

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА

ЧАСТОТНОЙ ИНФОРМАЦИИ

Изобретение относится к области передачи дискретной информации и может быть применено для передачи дискретных сообщений по каналам связи от источников информации к

ЭЦВМ, а также для передачи информации в низовых звеньях автоматизированных систем управления производством.

Известны многочастотные устройства передачи дискретных сообщений, содержащие иточники информации, модуляторы, передатчики, на приемной стороне приемники, дешифратор и фильтры (1).

Однако такие устройства не обеспечивают высокой скорости передачи информации.

Известно также устройство (2), содержащее на передающей стороне источник информации, подключенный через последовательно соединенные модулятор и выходной усилитель к прямому каналу связи, блснк повторения символов, принятых с ошибкой, и приемник сигналов квитирования, подключенный к обратному каналу связи, а на приемной стороне— параллельные цепочки из последовательно соединенных полосового фильтра, усилителя-ограничителя, приемника,и детектора с пороговым элементом. Одни концы цепочек подключены к прямому каналу связи, а другие концы — к входам дешифратора, .выход которого через последовательно соединенные выходной регистр, блок обнаружения ошибок и передатчик канала обратной связи соединен с каналом обратной связи. Выход дешифратора через последовательно соединенные элемент па.- -мяти и формирователь импульсов комленсации

5- помех подключен к управляющему входу всех . приемников, Однако это устройство имеет ограниченный диапазон регулирования длительности импульса гашения, что при большом уровне помех

1р может вызвать несовпадение момента смены посылок со временем окончания импульса гашения. В этом случае происходит либо не полное гашение предыдущей посылки, либо импульс гашения захватывает часть последующей посылки, что может привести к сбоям.

Особенно часто сбои происходят при передаче информации короткими посылками. В системах с обратной связью повторяются комбинации, которые приняты со сбоями, что за2Р метно снижает скорость передачи сообщений.

Цель изобретения — повышение скорости передачи многочастотных сигналов асинхронными системами, т. е. повышение быстродействия устройства.

25 Это достигается путем введения в устройство на приемной стороне цепочек из последовательно соединенных преобразователя частоты в напряжение, выпрямителя, элемента, фиксирующего уровень напряжения, и элемента

Зр преобразования, и элемент «ИЛИ». Входы це516084 почек подключены к выходам соответствующих усилителей-ограничителей, а выходы через элемент «ИЛИ» — к входу элемента памяти.

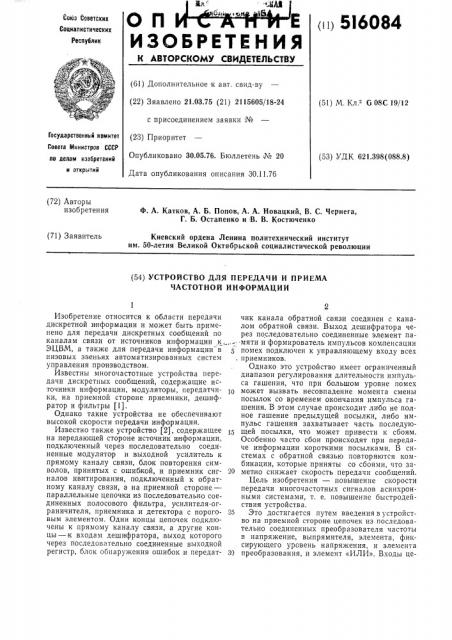

На фиг, 1 представлена структурная схема предлагаемого устройства, где 1 — источник информации; 2 — модулятор; 3 — выходной усилитель; 4 — канал связи; 5 и б — групповые полосовые фильтры; 7 и 8 — усилители-ограничители; 9 и 10 — демодуляторы; 11 и 12— приемники; 13 и 14 — детекторы с пороговым элементом; 15 — блок выявления моментов смены параллельно-последовательных посылок; 16 — элемент памяти; 17 — формирователь импульсов компенсации помех; 18 — блок формирования импульсов компенсации помех;

19 — дешифратор, 20 — выходной регистр;

21 — элемент «ИЛИ»; 22 — блок обнаружения ошибок, 23 — передатчик канала обратной связи; 24 — обратный канал связи; 25 — приемник сигналов квитирования; 26 — блок повторения символов, при нятых с ошибкой.

На фиг. 2 представлена структурная схема блока выявления моментов смены параллельно- последовательных посылок; на фиг. 3 — амплитудно-частотная характеристика преобразователя частоты в напряжение; на фиг. 4— временная диаграмма работы устройства совместно с блоком выявления моментов смены параллельно-последовательных посылок.

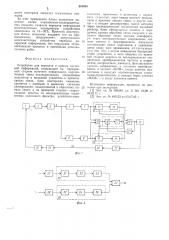

Блок выявления моментов смены параллельно-последовательных посылок включает в себя преобразователи 27 и 28 частоты в напряжение, к выходам которых подключены блоки 29 и 30 формирования сигналов «конец гашения», содержащие последовательно соединенные выпрямители 31, 32, элементы 33 и 34, фиксирующие уровни напряжения, и элементы

35 и 36 преобразования. Выходы блоков формирования сигналов «конец гашения»» подсоединены к входам элемента «ИЛИ» 37, выход которого связан с входом «конец гашения» блока 18 формирования импульсов компенсации помех.

Устройство работает следующим образом.

Передаваемый сигнал от источника 1 сообщений поступает в модулятор 2, где преобразуется в соответствующую данному каналу форму, усиливается усилителем 3 и поступает в канал 4 связи, На приемной стороне двухчастотные посылки разделяются групповыми полосовыми фильтрами 5, 6. Каждый фильтр выделяет одну из частот своей группы, на которую он настроен, и не пропускает частоту соседней группы, вследствие чего на выходе групповых фильтров имеются одночастотные сигналы соответствующей группы. Эти сигналы усиливаются и нормируются по амплитуде усцлителями-ограничителями 7, 8 и поступают на входы приемников 11, 12 частотных сигналов демодуляторов

9, 10. Приемники частотных сигналов выполнены на узкополосных коммутируемых фильтрах, согласованных с принимаемыми сигналами. Сигналы, выделенные прием никами частотных сигналов, детектируются детекто5

65 рами 13, 14 с пороговым элементом и после срабатывания пороговых элементов декодируются дешифратором 19. С выхода дешифратора снимаются комбинации прямоугольных импульсов в двоичном коде, которые заносятся в выходной регистр 20. Одновременll0 с этим с выхода элемента «ИЛИ» 21 снимается импульс, соответствующий моменту фиксации очередной посылки схемой приемника. Этот импульс переключает элемент 16 памяти блока 18 формирования импульсов компенсации помех. Формирователь 17 импульса компенсации помех начинает выдавать импульс гашения, который поступает на управляющие входы приемников 11, 12 частотных сигналов. Так как для передачи сообщений в данном устройстве используется неприводимый сменнопосылочный код, при смене посылок на входе приемника происходит смена частот хотя бы в одной из групп рабочих частот. При этом изменяется уровень сигнала на выходе одного из преобразователей 27 или 28 (фиг. 2), который после выпрямления соответствующим выпрямителем 31 или 32 поступает на элемент фиксации уровня напряжения (33 или 34) . Для пояснения работы преобразователей частоты в напряжение на фиг. 3 приведена амплитудно-частотная характеристика преобразователя первой группы частот в напряжение.

Таким образом, изменение уровня сигнала на выходе одного из преобразователей 27 или 28 фиксируется соответствующим элементом 33 или 34 фиксации уровня напряжения.

При изменении состояния элемента фиксации уровня на выходе элемента 35 или 36 преобразования появляется импульс, соответствующий смене посылок, который через элемент

«ИЛИ» 37 (фиг. 2) переключает элемент 16 памяти блока 18 формирования импульсов компенсации помех. Формирователь импульсов компенсации помех отключается, а импульс гашения с управляющих входов приемников частотных сигналов снимается.

На фиг. 4 представлена временная диаграмма работы многочастотного асинхронного устройства передачи дискретных сообщений совместно с блоком 15, где U,,— входной сигнал; Уф„Уф, — напряжения на выходах первого и второго фильтров приема частот первой группы; U»< — сигнал на выходе элемента «ИЛИ» 21; Ур — сигнал на выходе преобразователя частоты в напряжение;

U; — сигнал на выходе элемента «ИЛИ» 37;

U, сигнал на выходе формирователя импульсов компенсации помех.

Блок 22 обнаружения ошибок контролирует принятые комбинации по выбранному критерию. В случае обнаружения ошибок в принятой комбинации передатчик 23 канала обратной связи осуществляет переспрос знака, принятого с ошибкой. Сигнал переспроса воспринимается приемником 25 канала обратной связи и с помощью блока 26 повторения символов, принятых с ошибкой, прово516084

Щг. 1

Дуг. Z дится повторная передача пскажеш ых символов.

3а счет применения блока выявления моментов смены параллельно-последовательных посылок, скорость передачи информации многочастотным асинхронным устройством повысилась на 15 — 20%. Простота конструкции блока позволяет внедрить его на промышленных предприятиях, выпускающих многочастотные устройства передачи дискретной информации, без нарушения технологического процесса и проведения дополнительных работ.

Формула изобретения

Устройство для передачи и приема частотной информации, содержащее на передающей стороне источник информации, подключенный через последовательно соединенные модулятор и выходной усилитель к прямому каналу связи, блок повторения символов, принятых с ошибкой, и приемник сигналов квитирования, подключенный к обратному каналу связи, а на приемной стороне — параллельные цепочки из последовательно соединенных полосового фильтра, усилителя-огран чителя, приемника и детектора с пороговь м .=:лемептом, одни концы цепочек подключены к прямому каналу связи, а другие концы — к входам дешпфратора, выход которого

5 через последовательно соединенные выходной регистр, блок обнаружен я ошибок и передатчик канала обратной связи соединен с каналом обратной связи, выходы дешифратора через последовательно соединенные эле10 мент памяти н формирователь импульсов компенсации помех подключен к управляющему входу всех приемников, отличающеесяя тем, что, с целью повышения быстродействия устройства. в него введены на прием15 ной стороне цепочки из последовательно соединенных преобразователя частоты в напряжение, выпрямителя, элемента, фиксирующего уровень напряжения, и элемента преобразования, и элемент «ИЛИ», входы цепочек под20 ключены и выходам соответствующих усилителей-ограничителей, а выходы через элемент

«ИЛИ» — к входу элемента памяти.

Источники информации, принятые во вни25 мание при экспертизе: (1) Авт. св. № 366489, кл. G 08с 19/28 от

08.02.71 г. (2) Авт. св. № 490153 от 05.07.69 г.

516084

o,þ б0 (лгц) Уду 1

Корректор О. Тюрина

Редактор И. Грузова

Заказ 2320/1 Изд. № 1717 Тираж 830 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, »К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 8ых оЪ» max

7,О

//,80 б92 ///// 7/////,/b /,///

Р((г, 7

Составитель Н. Лысенко

Техред М. Семенов