Дискретный синхронизатор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е нн 516I72

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВМДЕТЕДЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 11.11.73 (21) 1969263,. 09 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.05.76. Бюллетень ¹ 20

Дата опубликования описания 02.08.76 (51) Ч Кт"- Н ОЗВ 3 04

Н 041 7/02

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДЕ, 621.394.662 (088.8) (72) Автор изобретения

H. С. Лобов (71) Заявитель (54) ДИСКРЕТНЫЙ СИНХРОНИЗАТОР

Изобретение относится к радиотехнике и может использоваться в радиотехнических импульсных системах при приеме дискретной информации.

Известен дискретный синхронизатор, содержащий последовательно соединенные задающий генератор, схему добавления-вычитания, делитель частоты, фазовый дискриминатор, к другому входу которого подключен входной блок, и реверсивный счетчик, выходы которого подключены к входам схемы добавления-вычитания и задающего генератора, кроме того, выход делителя частоты подключен к одному из входов регенератора.

Однако в известном дискретном синхронизаторе не сохраняется постоянная полоса подстройки фазы.

Цель изобретения — сохранение постоянной полосы подстройки фазы.

Для этого в предлагаемый синхронизатор введены распределитель записи, блоки памяти ч узел усилителей-ограничителей, при этом выходы распределителя записи через соответствующие блоки памяти подключены к входам узла усилителей-ограничителей, выход которого подключен к входу входного блока, вход распределителя записи соединен с входом регенератора, а дополнительный выход реверсивного счетчика подключен к управляощему входу задающего генератора, выход которого подключен к синхронизирующим входа м блоков п а мяти.

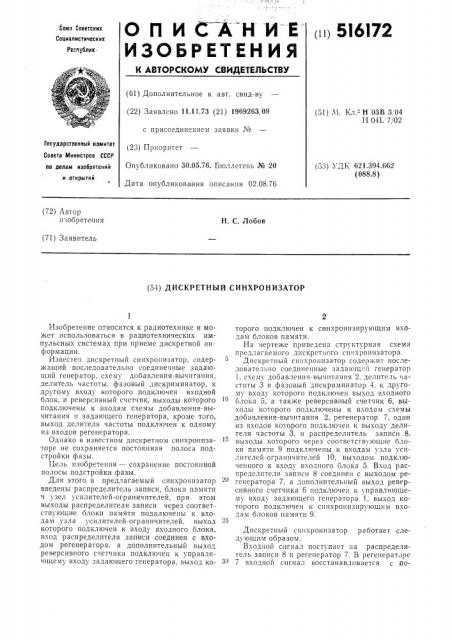

На чертеже приведена структурная схема предлагаемого дискретного синхронизатора.

Дискретный синхронизатор содержит последовательно соединенные задающи! I генератор

1, схему добавления-вычитания 2, делитель частоты 3 и фазовый дискриминатор 4, и другому входу которого подключен выход входного блока 5, а также реверсивный счетчик 6, выходы которого подключены к входам схемы добавления-вычитания 2, регенератор 7, один из входов которого подключен к выходу делителя частоты 3, и распределитель записи 8, выходы которого через соответствующие блоки памяти 9 подключены к входам узла усилителей-ограничителей 10, выходом подключенного к входу входного блока 5. Вход распределителя записи 8 соединен с выходом регенератора 7, а дополнительный выход реверсивного счетчика 6 подключен к управляющему входу задающего генератора 1, выход которого подключен к синхронизирующнм входам блоков памяти 9.

Дискретный синхронизатор работает следующим образом.

Входной сигнал поступает на распределитель записи 8 и регенератор 7. В регенераторе

30 7 входной сигнал восстанавливается с по516" 72

Составитель А. Кузнецов

Редактор Е. Караулова Техред Т. Курилко Корректор P. Юсипова

Заказ 1584, 4 Изд. ¹ 1436 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и огкрытии! 13035, Москва, К-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2 мощью синхроимпульсов с делителя частоты

3 до нормированной длигсльности и поступает па выход дискретного синхронизатора.

Распределитель записи 8 в моменты прихода фронтов входных посылок поочередно записывает в блоки памяти 9 фазу приходящего сигнала, которая запоминается блоками памяти 9. Число блоков памяти 9 нечетное.

В узле усилителей-ограничителей 10 импульсы с блоков памяти складываются, усиливаются и поступают во входной блок 5.

Входной блок 5 выделяет импульсы фронтов поступающих импульсов и выдает их на фазовый дискриминатор 4, который с помощью импульсов с делителя частоты 3 определяет величину и знак расфазировки между синхроимпульсами и входными посылками. Импульсы расфазировки с фазового дискриминатора 4 усредняются реверсивным счетчиком 6 и поступают на схему добавления-вычитания 2 для корректировки фазы синхронизирующих импульсов, которые получаются от деления частоты задающего генератора 1 делителем чаCTGTbI 3.

Если частота задающего генератора 1 отличается от частоты манипуляции входного сигнала, то с реверсивного счетчика 6 на задающий генератор 1 поступает сигнал, подстраивающнй частоту задающего генератора 1.

Формула изобретения

Дискретный синхронизатор, содержащий последовательно соединенные задающий генератор, схему добавления-вычитания, делитель частоты, фазовый дискриминатор, к другому входу которого подключен входной блок, и реверсивный счетчик, выходы которого подключены к входам схемы добавления-вычитания и задающего генератора, кроме того, выход делителя частоты подключен к одному из входов регенератора, отличающийся тем, что, с целью сохранения постоянной полосы подстройки фазы, введены распределитель записи, блоки памяти и узел усилителейограничителей, при этом выходы распределителя записи через соответствующие блоки памяти подключены к входам узла усилителейограничителей, выход которого подключен к входу входного блока, вход распределителя записи соединен с входом регенератора, а дополнительный выход реверсивного счетчика подключен к управляющему входу задающего генератора, выход которого подключен к синхронизирующим входам блоков памяти.