Коммутатор

Иллюстрации

Показать всеРеферат

(ii) 5I6l92

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ бова Советских

Социалистических

Реслублик (61) Дополнительное к авт. свид-ву (22) Заявлено 03.06.74 (21) 2030610/26-21 с присоединением заявки № (51) М. Кл з Н ОЗК 17/02

Совета Министров СССР по делам изобретений и открытий

Опубликовано 30.05.76. Бюллетень ¹ 20

Дата опубликования описания 27.07.76 (53) УДК 621.382(088.8) (72) Авторы изобретения

И. Я. Беленький и И. В. Чеблоков (71) Заявитель (54) КОММУТАТОР

Изобретение относится к устройствам автоматики и измерительной техники и предназначено для использования в коммутаторах измерительных сигналов.

Известны коммутаторы, содержащие измерительные ключи, которые соединяют соответственно четные и нечетные измерительные входы с двумя выходами коммутаторов, счетчики каналов и групп каналов, соедпнепшыс последовательно по счетным входам, дешифраторы каналов и групп каналов, входы котоpbIx соединены с выходами соогветству|ощпх счетчиков, а выходы сседш;епы с матрш,ей включения выбранного канала в выбранной группе, и задающий генератор.

В известны.: коммутаторах возможность изменения числа полюсов коммутации отсутствует вообще или может производиться только непосредственно изготовителем по заказу потребителя.

Цель изобретения — автоматизация изменения числа полюсов коммутации и тем самым — расширение функциональных возможностей коммутатора.

Это достигается тем, что в предлагаемом коммутаторе выходы дешифратсра групп каналов соединены с программным устройством, выход которого соединен с управляющим входом дешифратора каналов и входом первого элемента «И», второй вход которого соединен

ГосУдаРственный комитет (23) приоритет с выходом задающего генератора, а выход— с входом элемента «ИЛИ», и входом инвертора, а выход инвертора соединен с управляющим входом дополHíòåëьного ключа, который включен между вы;одами комму татора, входом второго элемента «И», второп вход которого соединен с выходом задающего генератора, а выход — со счетным входом триггера, и входом третьего элемента «И», второй вход которого соединен с выходом триггера, а выход — с вторым входом элемента «ИЛИ», выход триггера соединен с входом дешифратора каналов, а выход элемента «11ЛИ» — с входом счетчика каналов.

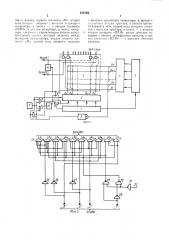

15 На фиг. 1 представлена схема предлагаемого коммутатора; на фиг 2 — схема дешифратора с управляющим входом.

В состав коммутатора входят счетчик 1 на

V:2 каналов; счетчик 2 на М групп каналов;

20 дешифраторы 3 и 4 на Л и М положений, выходы которых образуют матрицу 5 включения выбранных каналов в выбранной группе, имеющую Л )(М измерительных входов, распр»деленных на два выхода, объединяющих соот25 ветственно нечетные и четные входы, причем дешифратор каналов 3 имеет дополнительный управляющий вход; программное устройство

6, в которое вводятся Л1 выходов дешифратора 4 групп каналов; задающий генератор 7;

30 три элемента «И» 8, 9, 10; элемент «ИЛИ» 11;

65 инвертор 12; счетный триггер 13 и дополнительный ключ 14, аналогичный измерительным ключам коммутатора и объединяющий два выхода матрицы 5, причем выход программного устройства 6 соединен с входом инвертора 12, управляющим входом дешифратора 3 и входом элемента «И» 8, второй вход которого соединен с выходом задающего генератора 7, а его выход — с одним из входов элемента «ИЛИ» 11, выход инвертора 12 соединен с управляющим входом дополнительного ключа 14, входом элемента «И» 9, другой вход которого соединен с выходом задающего генератора 7, а его выход — со счетным входом триггера 13; выход инвертора соединен также с входом элемента «И» 10, другой вход которого соединен с выходом триггера 13, а выход — с вторым элементом «ИЛИ» 11, выход триггера 13 соединен с входом дешифратора 3, а выход элемента «ИЛИ» 11— с входом счетчика каналов 1.

Если триггер 13, счетчики 1 и 2 находятся в исходном состоянии, то дешифраторы 3 и 4 выдают управляющие сигналы по первым выходам. Соответственно выбирается первый канал первой группы. Кроме того, управляющий сигнал дешифратора 4 поступает также в программное устройство б. В том случае, если для первой группы каналов не программируется увеличение числа полюсов коммутации, управляющий сигнал на выходе устройства б соответствует «нулевому» (низкому) логическому уровню. При этом элемент «И»8 закрыт, элементы «И» 9 и «И» 10 открыты от инвертора 12, который выдает также сигнал па заключение ключа 14, объединяющего выходы коммутатора; выход задающего генератора 7 подключен через элемент «И» 9 на вход счетного триггера 13, а выход последнего подключен через элементы «И» 10 и «ИЛИ» 11 на вход счетчика 1. Импульсы генератора 7 считаются триггером 13 и счетчиком 1, при этом дешифратор 3 поочередно выдает управляющие сигналы на выбор всех каналов первой группы. При выдаче сигнала переноса на счетчик 2 дешифратор 4 переходит во второе положение. В случае, если для второй группы каналов увеличение числа полюсов коммутации также не запрограммировано, работа повторяется аналогичным образом для второй группы каналов.

В случае, если для второй группы каналов запрограммировано увеличение числа полюсов коммутации, программное устройство 6 выдает управляющий сигнал, соответствующий «единичному» (высокому) логическому уровню. При этом открывается элемент «И» 8, от инвертора 12 закрываются элементы «И»

9 и 10, и генератор 7 через элементы «И» 8 и «ИЛИ» 11 подключается непосредсгвеино на вход счетчика 1, размыкается ключ 14, разъединяя выходы коммутатора, а наличие сигнала на управляющем входе дешифратора 3 обеспечивает включение сразу двух выходов дешифратора — первого и второго.

Дешифратор с управляющим входом (фиг. 2) показан на примере дешифратора двоично-десятичного кода 8421. Дешифратор состоит из элементов 15 — 24, инверторов 25—

28 и отличается от известных наличием двух элементов «И вЂ” НЕ» 29 и 30, которые по одному входу через инвертор 31 связаны с управляющим входом 32. Наличие на управляющем входе «нулевого» (низкого) логического уровня через инвертор 31 открывает элементы 29 — 30, и дешифратор как обычно на каждую комбинацию двоично-десятичног< кода 8421 отрабатывает по одному из выхо дов с первого по десятый.

Наличие же па управляющем входе «единичного» (высокого) логического уровня через ипвертор 31 закрывает элементы 29 — 30 и создает а их выходах также «единичный» логический уровень. Это приводит к одновременному включению сразу двух выходов дешифратора (печетного и четного) в зависимости от комбинации по входам «8», «4», «2», «1», В связи с изложенным выше при выдаче управляющего сигнала от программного устройства 6 происходит включение сразу двух выходов дешифратора — первого и второго.

Таким образом, происходит включение сразу двух измерительных ключей коммутатора, соответствующих измерительному каналу с удвоенным числом полюсов коммутации. Так как каждый измерительный ключ может иметь несколько полюсов коммутации (например, один, два, три), то общее количествополюсов может составить соответственно два, четыре, шесть.

Далее в процессе счета подключается последующие выходы дешифратора 3, пока счет. чик 1 не выдаст сигнала переноса и счетчик не перейдет в очередное положение.

Далее работа продолжается аналогичны. образом в соответствии с программой.

Таким образом, в процессе опроса каналов обеспечивается автоматическое удвоение числа переключаемых полюсов в измерительных каналах прп условии уменьшения в два раза числа каналов данной группы.

Формула изобретения

Коммутатор, содержащий измерительные ключи, которые соединяют соответственно четные и нечетные измерительные входы с двумя выходами коммутатора, счетчики каналов и групп каналов, соединенные последовательно по счетным входам, дешифраторы каналов и групп каналов, входы которых соединены с выходами соответствующих счетчиков, а выходы соединены с матрицей включения выбранного канала в выбранной группе, и задающий генератор, отличающийся тем, что, с целью автоматизации изменения числа полюсов коммутации, выходы дешифраторг групп каналов соединены с програмным устройством, выход которого соединен с управляющим входом дешифратора кана516192

УхФ-1 Nx /

15 лов и входом п рвого элемента «И», второй вход которог. соединен с выходом задающего генератора, а выход — с входом элемента

«ИЛИ», и входом ипвертора, а выход инвертора соединен с управляющим входом дополнительного ключа, который включен между выходами коммутатора, входом второго элемента «И», второй вход которого соединен с выходом задающего генератора, а выход— со счетным входом триггера, и входом третьего элемента «И», второй вход которого соединен с выходом триггера, а выход — с вторым

5 входом элемента «ИЛИ», выход триггера соединен с входом дешифратора каналов, а выход элемента «ИЛИ» — с выходом счетчика каналов.