Интегральный приемник бинарных сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

И ЗС БР ЕТЕ Н И Я

1111 516 I 98

Со1оз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 26.07.73 (21) 1950033, 09 с присоединением заявки зле (23) Приоритет

Опубликовано 30.05.76. Бюллетень М 20

Дата опубликования описания 09.07.76 (51) М. Кл. - Н 04В 1,10

H 041 27,!26

Государственный номитет

Совета Министров СССР по делам изобретений и открытий (53) Д1; 621.396.621 (088.8) (72) Авторы изобретения

H. В. Захарченко и Г. А. Пружина

Одесский электротехнический институт связи им. А. С. Попова (71) Заявитель (54) ИНТЕГРАЛЬНЫЙ ПРИЕМНИК БИНАРНЫХ СИГНАЛОВ

Изобретение относится к технт1ке передачи дискретной информации, в частности к устройствам регистрации бинарных символов, и ,мо кет использоваться для повышения .достоверности приема в основном для проводных каналов связи.

Известен интегральный приемник бинарных сигналов, преимущественно для проводных каналов связи, содержащий блок предварительной селекции символов с подключенными к 10 его входу последовательно соединенными детектором качества и линией задержки, а та .нке два интегратора, выходы которых через элемент сравнения соединены с выходным блоком. 15

Однако в известном приемнике наличие помех, напряжение которых превышает напряжение сигналов в пределах длительности символов, приводит к тому, что последний может быть принят неверно. 20

Целью изобретения является повышение достоверности приема при наличии помех.

Для этого в предлагаемом приемнике соответствующие выходы блока предварительной селекции символов соединены с входамп ин- 25 теграторов через элементы запрета, управляющие входы которых соединены между собой и с выходом линии задержки, причем входы синхронизации обоих интеграторов и элемента сравнения соединены с блоком предва- ЗО рптельной сслскцпп символов чсрсз блок поэлсмен пlого фазп1)овяни11.

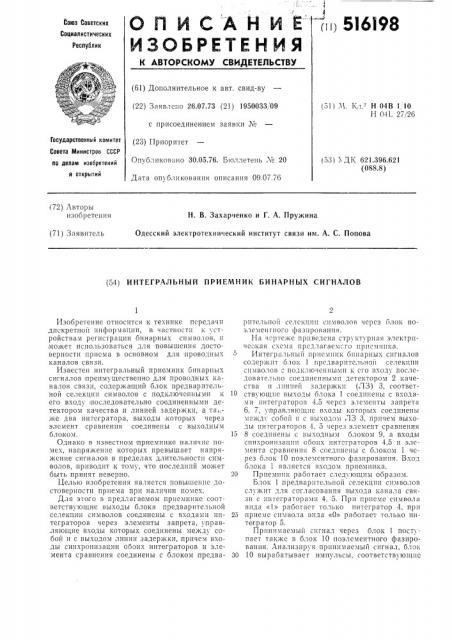

На чертеже приведена структурная элсктрпчеокая схема предлагаемого IIprri минка.

Интегральный Irprreirrlrrr бинарных сигналов содержит Олок 1 нрслварптс. Iьнон ce rer;rrrrrr символов с полключснньвмп к сго входу последовательно соелпнспнымп детектором 2 качества и линией задержки (ЛЗ) 3, соответствующие выхолы блока 1 соединены с входамп интеграторов 4,5 чсрсз элементы запрета

6, 7, управля1ощпс входы которых сослинены межд собой и с выходом ЛЗ 3, причем выходы интеграторов 4, 5 через элемент сравнения

8 соединены с выходным блоком 9, а входы синхронизации Обоих интеграторов 4,5 и элемента сравненп11 8 соединены с блоком 1 через блок 10 поэлемснтного фазпрованпя. Вход блока 1 является входом приемника.

Приемник работает следующим образом.

Блок 1 предварительной селекции символов служит для согласования выхода канала связи с интеграторами 4. 5. При приеме символа вида «1» работает только интегратор 4, прп приеме символа вила «О» работает только интегратор 5.

Принимаемый сигнал через блок 1 поступает также в блок 10 поэлементного фазирования. Анализируя принимаемый сигнал, блок

10 вырабатывает импульсы, соответствующие

516198

Формула изооретсния

Вх

Составитель Г. Теплова

Тсхред 3. Тараненко

Корректор А. Галахова

1 едактор Е. Караулова

Закал 1451/6 Изд. № 1410 Тираж 864 Подписное

Ц1-1ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2,краям .принимаемых символов, и синхронизирует работу интеграторов 4,5 и элемента сравнения 8. При этом в конце каждого символа импульсы, вырабатываемые блоком 10, выключают элемент сравнения 8 и обнуляют интеграторы 4, 5.

Сигнал с выхода детектора 2 качества через ЛЗ 3 поступает на управляющие входы элементов залрета 6, 7. При этом в основу работы детектора 2 качества заложен тот прин- 10 цип, что совокупность значений, принимаемого сигнала делится на три области: область значений, принадлежащих «1», область значений, принадлежащих «О», о бласть значений, где верный прием сомнителен с весьма большой 15 вероятностью, а величина задержки ЛЗ 3 выбирается в зависимости от того,,на сколько задерживается принимаемый сигнал в блоке 1.

Если детектор 2 качества не обнаруживает 0

;помех, приемник работает обычным образом.

В случае обнаружения,детектором 2 помехи он выдает соответствующий сигнал, элементы запрета 6 и 7 отключают входы интеграторов

4 и 5 от выходов блока 1, исключая из инте- 25 грирования те участки символа, которые поражены сильнодействующей помехой и которые с большой вероятностью могут быть приняты неверно.

Таким образом, исключая из ингсгрирования обнаруживаемые детектором 2 качества искаженные части символа, распознавание .последнего производится ло его неискаженным участкам, что при идеальных элементах схемы позволяет осущсствить верный прием при искажениях, стремящихся к 100%.

Интегральный приемник бинарных сигналов преимущественно для проводных каналов связи, содержащий блок предварительной селекции символов с подключенными к его входу последовательно соединенными детектором качества и линией задержки, а также два интсгратора, выходы которы.; через элемент сравнения соединены с выходным блоком, отл и ч а ю,шийся тем, что, с целью повышения достоверности приема при наличии помех, соответствующие выходы блока предварительной селекции символов соединены с входами интеграторов через элементы запрета, управляющие входы которых соединены между собой и с выходом линии задержки, причем входы синхронизации обоих интеграторов и элемента сравнения соединены с блоком предварительной селекции символов через блок поэлементного фазирования.