Устройство для вычисления квадратного корня из частного и произведения двух аргументов

Иллюстрации

Показать всеРеферат

(61) Дополнительное к авт, свид-ву— (51) N. Кл. Q 068 7/38 (22) Заявлено 29.06.73 (21) Х 9;- 9787 1 с присоединением заявки М(23) Приоритет—

Государстаенный камктет

Вааета Министраа СССР аа делам изобретений н атнрытий (43) Опубликовано05.06.76.Бюллетень @21 (53) УДК 681 325 5 (088.8)

) (45) Дата опубликования описания 16.09.76 (72) Авторы изобретения

A. Л. Рейхенберг и P. Я. Шевченко (71) Заявитель

<5 л-) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ ЧАСТНОГО И ПРОИЗВЕДЕНИЯ ДВУХ АРГУМЕНТОВ

Изобретение относится к области вычислитегьн.- " . техники и может быть использовано для аппаратурной peanêçàöèè подпрограммы вычисления элементарных функций в специагызированных 11ВМ с фиксированной запятой.

k"...вместно устройство д я вычисления к*м,цратного корня, содержашее накопительные сцвигаюшие регк=трь:, регистр памяти, блок управления элемент анализа знака и од-.

l0 норазряцнь" г комбинационные сумматоры.

Недостатком известного устрайс":ва яв . ляютс. : .,-;. и-.-гльные затраты вр мен:.: для одновременного вь.--ясления квацратного к .::- : з частного и произведения,цвух

И аргу! ! "-. ц ю .зобретения является повьш:ение бысгасдей"твия „стрс-;ства для одновременного вь,ч1".ленин кве.:;,,летного корня иэ част20 -. го л .-:.:.-.изведения. За цель достигается эа с ет того, и" ", :: .иженное устройство .цополнительно . содержит э.:ем=-нт анализа сходимости, накол:;"тельные сдвигеюшие регистры и одноо разряцный комбинационнв и сумматор. Управляюший вход одноразрядного комбинационного сумматора второго псевдоумножителя соединен с выходом накопительного сдвигаюшего регистра второго аргумента, а основной вхоц этого сумматора - с выхо 1 дом предпоследнего разряца накопительного сдвигаюшего регистра второго псевдоумножителя, выход которого соединен с управ- ляюшим входом оцноразрядного комбинационного сумматора псевдоделителя. Третий вход этого сумматора соединен с выходом накопительного сцвигаюшего регистра второго аргумента. Выходы всех разрядов накопительного сцвигеюшего регистра псевдоделителя соединены с входами элемента анализа t схоцим-.-",ти, выход которого соеди-, нен с входом сброса элемента управления.

Алгорит . извлечения квадратного корня иэ частного и произведения основан на следующих рекурентных соотношениях для двоичной системы стеисления, обеспечиваюших наиболее простую структуру реализации:

517021 3 г -2(j>) м =X. 53 =Х-Е =(d - О -Y2 . М О

0 + 3

13

+i гни й„>0 и = а о— J O„ „,„„„tr, )i 3 -1 rr g 3 с()

U -О. 0 -2, 2 = +, Y 2 0„

-(J+>) У„ -2()и)

0 J+1 2

-(пн) - Д ),,(щ

-6 2 -. и +,-2+II,2, z - L>/v

Все указанные, вычислительные операциями

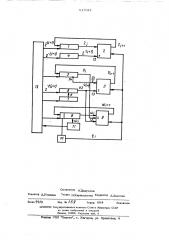

it могут быть реализованы в структуре, со.цержащей три накопитегпных сдвигающих регистра, три одноразрядных сумматора и И ряд регистррв сдвига, На чертеже представлена блок-схема устройства для получения квадратного корня из частного и произведения, где обозначены накопительный сдвигающий ре- 2О гистр 1 значения квадратного корня из частного; одноразрядные. сумматоры 2, 3 на два входа; одностороннюю память 4, накопительный регистр 5 второго псевцоумножи тели для значения квадратного корня из произведения, сдвигающий регистр 6, вход- ной регистр 7 аргумента Y накопитель ный сдвигающий регистр 8 псевдоделитэля; одноразрядный сумматор 9 на три входа; элемент анализа знаиа псевдочастного 10, элемент анализа сходимости очередного приближения аргумента 11 и элемент управления 12.

Параллельно-последовательная,структура устройства обладает относительно высокой однородностью и состоит из стандартных цифровых элементов одноразряцных сумматоров на два и на три входа, сдвига оP щих регистров, элементов совпадэния, односторонней памяти и,элементов управленя я.

Значение аргумента Х (причем 0:; Х 1): заносится в регистр 8, состоящий из (Ф + Ф,,) разрядов, где 1 - число 45 разрядов аргумента, у ь — число допол нительных разрядов для компенсации погрешности.

Значение аргумента У (причем для данной записи ara,оритма 1 У. <,2) за- 59 носится,во входной и -разрядный регистр 7, содержимое которого сцвигается (В + & )-разряцным регистром 6 л поцае ся на управляющий вхоц 13 сумматора 3 и оцновременно на третий вход сумматора 55

9.

Иыхоц предпослецней ячейки накопительного регистра 5 второго псевдоумножцтеля подан на основной вход одноразрядного сумматора 3, выход которого подк,почен 60 с ко вхоцу накопительного регистра 5. Выход регистра 5 подключен к входу 13 однб)зазряцног о сумматора 9.

К основному входу сумматора 9 поцключен выход накопительного сдвигающего регистра 8 псевдоделителя, z входу которого подключен выход суммаго-, ра 9 псевдоделителя. Знаковый разряд накопительного сдвигающего регистра 8 псевдоделителя соецинен с элементом 3 0 анализа знака псевцочастного. Выход элемента 10 анализа знака соединен q управляющими входами всех сумматоров.

Выходы всех ячеек накопительного сдвигающего регистра 8 псевдоделителя со» единены с параллелью ми,входами элемента анализа сходимости 11, выход которого соецинен с входом сброса элемента управр ления 12.

Выход регистра 1 первого псевдоумножителя соединен с основным входом сумматора 2, выхоц которого соединен с вхоцоМ регистра первого псевдоумножителя. Ко входу 13 сумматора 2 подсоединен выход односторонней памяти, в) которой

I хранятся константы вида 2 где =0 1,..., ft

Управление процессом вычисления путем подачи соответствующих тактовых сдвига ощих импульсов, осуществляется элементом управления 1 2.

Г1араллельно-последовательная структура определяет параллельное вычисление приве:.

Ъ денных рекуррентных соотношений алгоритма, каждое из которых вычисляется последовательно, и каждой итерацйи,за (@, + Q) тактов. ©

Число итераций для требуемой точности вычисления (1 О -1 6 дв. разряцов) при решении задач управления на единицу больше числа разряцов.

В первой итерации из соцержимого накопительного сдвигающего регистра 8 псевдоделителя вычитается сдвинутое,на разряда вправо от цвоичйой запятой значе- ния второго аргумента У. Но знаку полученной разности определяется в элементе анализа знака псеццоделимого очередная цифра ) псевдочастного в специальном элементе счисления (+ 1, - 1 ). Если очеред=

J ное прчближение значения аргумента больше самого аргумента Х, то разность в рег ре псевдоделения меньше нуля, и очередная (на следующей итерации) цифра псездочастного равна -1 . При этом з оги: разрядных сумматорах 2 и 3 выполняется операция вычитания, а по управляющему вход" трехвходового с j""мматора 9 » «cllE. ,рация сложения.

517021

В начальном состоянии в регистрах 1 (первого) и . 5 (второго) псевдоумножите« лей содержимое равно нулю. В первой итерации в регистр 1 первого псевдоумножителя записывается с соответствующим эна- 6 ком значение первой константы (2 ), -1 второго аргумента У. Процесс псевдоумчожения аналогичен умножению и необходим для преобразования очере,цной цифры псевдочастного " в двоичную систему

J счисления значений квадратного корня.иэ частного (регистр 1 ) и произвецения (регистр 5).

При значении очередного приближения аргумента меньше действительного Х оче- 15 реднея цифра псевцочастного 9 ..= =+1 . 1 и перемены операций в сумматорах не пре исхопит.

Пpoцcсc вычисления к&жцой HTepGllHH p повт.ряется (ф + 1) раз. В конце процеосе вb:.ÿ"ëåíèÿ в регистрах 1 и 5 записаны . значения указанных функций.

Быстродействие предлагаемого устройства с параллельно-последовательной . структурой определяется в тактах соотношением г: 2 (:;, + р ) и значительно больше чем, и использовании известных уст- . ойств, Для лодавляюшего большинства эначе- щ ний аргу;агентов точное значение .вычисляемых функций получается при числе итера- ц-.".;леньше (l5 + 1, . Для сокрашения времен вычисления в- структуру введен элемент анализе -.".ходимссти 11, прецставляю 35 ций собой элемент сравнения с нулем со-,. держимого регистра 8 псевцоделителя, Р случае когда все резгппы регистра 8 псеьподелителя незнечешие, с выхода элемен-.а анализа выдается =:r-. Hàë сброса 40

".-.-гановки) элемента упрев ения на сле» дуюшей герации, чем достигается асинх» ренн,. и режим элемента управления, Например при Х = 0,5 и У вЂ” — 1,0 для получения точного значения функции необходима 45 .=оль. о адге чтереция. Для четыр х значе, ний аргументов необхопимы две итерации Й т.,ц. Значение квапратного корня из произве,дения в накопительном регистре 5 псевдо1умножителя в конце процессе сдвинуто вправо HB (f1 + 1 ) раэряпов поэтому !,trâoè÷HRÿ запятая при чтении также пере,носится вправо на (tl + 1 ) разрядов, структурным путем.! Формула изобретения

Устройство,цля вычисления квацрат,ного корня из частного и произведения двух о аргументов, содержащее накопительные

1, сдвигаюшие регистры и регистр памяти, упревляюшие вхоцы которых соецинены с ! соответствуюшими выхоцами блока управj ления, однорезряцные комбинационные . ! сумматоры, управляющие входы которых соединены с выходом элемента анализе !

) знака,, вход элемента анализа знака соеди1 нен с выхоцом знакового разрцще накопи-, !

1 тельного сдвигаюшего @егистре псевдо1, делителя, о т л и ч а ю ш е е с я тем, t что, с целью повышения быстродействия, !

; оно дополнительно содержит элемент ана, лиза сходимости, накопительные спвигаю1шие регистры и одноразряцный комбинацион

1 ный сумматор„причем упревляюший вход

1 опнорезрядного комбинационного сумматора второго псевдоумножителя соединен с вы! ходом накопительного сдвигаюшего регистре второго аргумента, а основной вход этого сумматора — с выхоцом предпоследнего

1разряца накопительного сдвигеюшего регист

|ра второго псевдоумножителя, выход кото-

)рого соединен с управляюшим входом одно-. резряцного комбинационного сумматора псевподелителч; третий вход этого суммато1

1ре соединен с выходом накопительногс сдви=

jгаюшего регистра ворога аргумента, вы:.ходы всех резряпов накопительного сцвига1юшего регистра псевдоцелителя соединены

jco входами элемента анализа схопимости, 1

I выход которого соединен со вхоцом,сбруи. ,блока управления.

517021

Ивд, а /53 Ти рак 864 Подписное

3аквв 5979

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушсквя иаб., 4

Филиал РПП «Патент, r. Ужгород, уд. Проектная, 4

Составитель И" Данущова

Редактор Л.уте>ша Техред ИЯарандашова «рректор А.Дзесова