Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИКАНИЕ «»идол

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву (22) Заявлено 16.01.75 (21) 2097942/18-24 (51) М. Кл. G 11 С19/00 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 05.06.76. Бюллетень № 21 (53) УДК 681 .327.6 (088.ь> (4б) Дата опубликования описання18.07.77

Госудврстеенный номитет

Соввтв Министров СССР во делам изобретений и отнрытий (72) Авторы изобретения В. А, Скрипко, Ю. Б. Толшин, А. В. Невольниченко и И. Х. Габбасов (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Известно запоминающее устройство (ЗУ), со держащее поразрядно соединеинные входной, ад. ресные н основные регистры сдвига, первый элемент "ИЛИ", входы которого подключены к выхо. дам входного регистра, а выход — к первому элементу Задержки, счетчик, вход которого соедзгнен с выходом второго элемента "ИЛИ"., а выход— с одним иэ входов коммутатора, элемент "Запрет" и второй и третий элементы задержки.

Это устройство обеспечивает сжатие "пустых" слов и кадров, Вместо. "пустого" сообщения в канал связи передаются его признаки: начало и окончание такого слова. А "пустые" кадры не частое явление, как правило, в кадре хотя бы одно слово, но — значащее (для больших кадров), и приходится передавать весь кадр. Поэтому на два, три значащих слова в кадре, содержащем, например, 500 слов придется передавать сотни признаков

"nycwx" слов. Таким образом, для больших кадров объем служебной информации остается очень большим. Кроме того, признаки слов и разряды, несущие сведения о значении таких слов, приходится передавать вперемежку, что требует специальной

"подкраски" признаков слов для их выделения приемным комплексом с целью дешифрирования информации.

Это сужает область применения известного устройства.

Чтобы сократить объем служебной информации в кадре, а также избежать необходимости

"подкраски" ее, нужно отделить признаки "пустых" и значащих слов от полезных сообщений и сформировать из таких признаков адресную посыл1ð ку, следующую в начале или конце кадра.

Предложенное устройство отличается от известногоо тем, что оно содержит дополнительный коммутатор, элемент "И", блок формирования признаков выборок и триггер, один вход которого лод1я ключен к выходу первого элемента "ИЛИ", другой к выходу элемента "Запрет", вход которого соединен с выходом первого элемента "ИЛИ".

Выходы триггера соединены со входами второго элемента "ИЛИ" и через второй элемент задержки-ур со входами блока формирования признаков выборок, выходы которого подключены ко входам коммутатора, а вход соединен с выходом второго элемента "ИЛИ", входом счетчика и управляющим входом дополнительного коммутатора, выходы ко. аб торого подключены к управляющим входам ком.

517052 мутатора, Один вход второго элемента "ИЛИ" соединен с выходом элемента "И", входы которого подключены к выходам счетчика. Вход дополнительного коммутатора соединен с выходом третьего элемента задержки.

Это позволяет расширить область применения устройства.

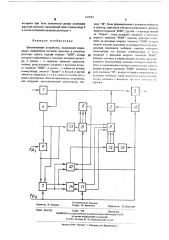

На чертеже изображена блок — схема предложен- ного устройства.

Устройство содержит входной 1, основные 2 и адресные 3 регистры сдвига, первый элемент

"ИЛИ" 4, элемент "И" 5, элемент "Запрет" 6, триггер 7, счетчик 8, коммутатор 9; второй элемент

"ИЛИ" 10, блок формирования признаков выборок 11, дополнительный коммутатор 12, первый 13, второй 14 и третий 15 элементы задержки н элемент

".И" 16.

Один вход триггера 7 подключен к выходу элемента "ИЛИ" 4, другой — к выходу элемента

"Запрет" 6, вход которого соединен с выходом элемента "ИЛИ" 4. Выходы триггера 7 соединены со входами элемента "ИЛИ" 10 н через элемент задержки 14 со входами блока 11, выходы которого нодключеиы ко входам ком му тат ора 9, а в ход— к выходу элемента "ИЛИ" lO, входу счетчика 8 и уиравлнющел1у входу коммуиаора !2, выходы ко. торого иодклю сны к уиравллннцилг входам коммутатора 9. Один вход элемента "ИЛ!Р 10 соещшен с выходом элемента "И" 5, входы которого подкл очены к выходам c

Рассмотрим принцип pa5on r устройства при емкости счетчика 8, равной 7. Аирес (признак) кадра с выхода регистра 1 поступает в первьш. регистр 2, а затем. автоматически переписывается из регистра в регистр и следует к выходу таких регистров. Одновременно этот адрес поступает и на вход элемента "ИЛИ" 4, При этом на era выходе появляется сигнал существешгой выборки. Этот сигнал поступает в счетчик 8, в котором записывается символ единицы, проходит на вход запрета элемента Запрет" 6, поступает на один вход триггера 7, оостряние которого не изменяется.

Допустим, что очередные четыре выборки также значительны, .тогда. в счетчике 8 будет записано число 5 (код 101).

Предложим, что шестая выборка стала "пус той", т.е, во всех разрядах данной выборки-символы нулей. Такая выборка в регистрах 2 на записывается, и на выходе элемента " ИЛИ" 4 сигнала нет.

Дри этом тактовый сигнал ТИ проходит через, элемент "Запрет" 6 на его выход и поступает на другой вход триггера 7, который перебрасывается, и иа его выходе появляется сигнал. Он проходит через элементы ".ИЛИ" 10 считывает код числа из счетчика 8. Признак значимости из блока 11 (код 1) поступает иа управляющий вход коммутатора 12 в качестве сигнала продвижения. На выходе коммутатора 12 появляется сигнал, и код 1101 записывается в разрядах первого регистра 3. Сигнал с

l0 выхода триггера 7 поступает также через элемент задержки 14 блока 11.

Одновременно с выхода элемента "Запрет" 6 сигнал через элемент задержки 13 поступает на счетный вход счетчика 8, и в нем эаписынаетсн код единицы. Допустим, что следующие выборки также

"пустые", поэтому тактовые сигналы ТИ с выхода элемента "Запрет" б поступают на вход триггера 7, состояние которого не изменяется, Одновременно

ТИ поступают на вход счетчика 8, который подсчитывает их, Предположим, что последовательно прошло 7 "пустых" выборок, и счетчик 8 переполнился (код 11!). В этом случае элемента "И" S формирует. сигнал, поступающий в элемент "ИЛИ" 10. Иа его выходе появляется сигнал, который ироходит на входы счет шка 8 н блока 11. В результате с их выходов иа вход коммута1ора 9 поступает код

Ol l l. Одновреме)и1о с выхода элемента "ИЛИ™ !О сигнал продвижения проходит на управляющий вход коммугаfopa!2, н на его выходе появляется сигнал, поступающий иа соответствующий управляющий входкоммутатора 9. Код0l l! записывается в соответствуюишх разрядах регисторн 3. В з1ом случае ни в триггере 7, ни в блоке !1 никаких нэл1енений не происходи r, лозовому следующая

"пустая" выборка з;ащсываетсн как символ единицы в счетчике 8, а сигнал с выхода элемента "Запрет" б, иос уииищий иа вмод триггера 7, не вызывает изл1еиеиий.

Предиопо ы м, аТ0 чвтыриадцатан в ыборка иришла значимой (T.е. хотн бы в одном из ее разрндов записан символ единицы). Оиа записывается в ре. гистрах 2, и на выходе элемента "ИЛИ" 4 появлнется сигнал, который поступает на вход элемента

"Залрет" 6 и закрывает его, проходит на вход триггера 7 н перебрасывает efo,и íà его выходе появляется сигнал. Этот сигнал через элемент

"ИЛИ" 10 считывает из счетчика 8 код числа 001 „из блока ll признак "Пустых" выборок (в данном

40 примере сигнала нет, что соответствует коду О). С выхода элемента "ИЛИ" 10 он проходит также на управляющий вход распределителя 12, íà его выходе появляется сигнал, и код 0001 записывается в соответствующих разрядах адресных регистров 3.

4б Сигнал с выхода триггера7 поступает такжь, через элементы задержки 14 в блок 11. Одновре-З .менно с выхода элемента ™ИЛИ" 4 сигнал через элемент задержки 13 проходит на вход счетчика 8, и в нем записывается код 1 и т.д.

50 . В момент окончания кадра в счетчике 8 может оставаться какое-то число. Поэтому сигнал окончания кадра ТИ поступает на вход элемента

"ИЛИ" 10, который формирует сигнал считывания, и из счетчика 8 и блока 11 соответствующий код

1 бб поступает на вход коммутатора 9, Этот сигнал проходит на вход коммутатора 9, и подготавливает коммутатор 9 для записи поступившего на его вход кода в регистры 3. Кроме того, сигнал окончания кадра ТИ возвращает в исходное состояние триггер7, коммутатор 12 и блок!!, на выходе

517052

Составитель В. Рудаков

Техред М. Левицкая

Редактор Л. Утехина

Корректор П. Ковалева

Тираж 756 Подписное

IlHHHflH Государственного комитета Совета Министров СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„д, 4/5

Заказ 926/132 филиал ППП "Патент", r, Ужгород, ул. Проектная, 4

Ф которого при этом появляется сигнал окончания адресной посылки, проходящий через коммутатор 9 в соответствующие разряды регистров 3.

Формула. изобретения

Запоминающее устройство, содержащее поразрядно соединенные входной, адресные и основные регистры сдвига, первый элемент "ИЛИ", входы которого подключены к выходам входного регистра, а выход — к первому элементу задержки, счетчик, вход которого соединен с выходом второго элемента "ИЛИ", а выход — с одним из входов коммутатора, элемент "Запрет" и второй и третий элементы задержки,о тли ч а ющ е ес ятем, что, с целью расширения области применения устройства, оно содержит дополнительный коммутатор, элемент "И", блок формирования признаков выборок и триггер, один вход которого подключен к выходу первого элемента "ИЛИ", другой — к вы коду эле мен. та "Запрет", вход которого соединен с пыхоцом первого элемента "ИЛИ", выходы Л)ипсра 00e!v)иены со входамн второго элемента "ИЛИ" и через второй элемент задержки со вход«ми блока форин ровання признаков выборок, выходы которого подключены К0 входам коммутатора, а и Aоц р соединен с выходом второго элемеитв 1331lf входом счетчика и управляющим вхоцом цоаО) ии. тельно«о коммутатора, выходы ко«орого лоцклн) че«лл к у)1раеляющ1«м Входам кОмму«ан2ра, акции иэ входов второго элемента "ИЛИ" соединен с Выхоаб цом элемента "И", входы которого цоцклкв сi «4 к пыхоцам счетчика; вход цоио)и)и(сяьц(л О комг гута )0))а 00ецииен с ВыхОдОм 1рс)! (I () элс! 1сп ) а задержки.