Устройство для управления однофазным тиристорным инвертором

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

„„517133

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 07.06.74 (21) 2032866/Π— 7 с присоединением заявки № (23) Приоритет (43) Опубликовано 05.06.76, Бюллетень № 21 (45) Дата опубликования описания 05.07.77 (ьц и. к.

Н 02 P 13/18

Гасударственный комитет

Соввтв Министров СССР

II0 долаи изобрвтений и открытий (53) УДК

621.316.727 (088.8) Э. Н. Гречко, В. Е. Тонкаль, Л. П. Мельничук и Д. С. Вертелецкий (72) Авторы изобретения

Институт электродинамики АН Украинской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОДНОФАЗНЫМ ТИРИСТОРНЫМ

ИНВЕРТОРОМ

Предлагаемое изобретение относится к однофазным инверторам, формирующим ступенчатую кривую выходного напряжения путем коммутации вторичных обмоток трансформатора.

Известны устройства управления такими инверторами.

Недостаток известных устройств заключется в ограниченном диапазоне работы на активно-индуктивную нагрузку.

В предлагаемом устройстве для управления однофазным инвертором указанный недостаток устраняется благодаря тому, что к выходу задающего генератора подсоединен триггер, первый формирователь коротких импульсов запуска тиристоров и последовательно включенные первый элемент задержки, регулятор длительности импульсов, второй элемент задержки и второй формирователь коротких импульсов запуска тиристоров, второй вход триггера подключен к выходу второго элемента задержки, а выход триггера к формирователю широких импульсов запуска тиристоров, вторые входы схем совпадения соединены с выходом регулятора длительности импульсов, а выходы схем совпадения связаны с цепями управления тиристоров, второй выход регулятора длительности импульсов соединен со входами четырех дополнительных схем совпадения, второй вход каждой из которых соединен, соответственно, с выходами первой, второй, шестой и седьмой ячеек пересчетной

5 схемы, а третий вход каждой из схем совпадения соединен с выходами датчиков тока в силовой цепи.

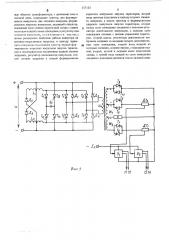

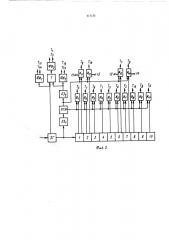

На фиг. 1 приведена силовая схема инвертора; на фиг. 2 — устройство для управления инвертором, 10 на фиг. 3 — диаграмма работы устройства управления и инвертора.

Силовая схема инвертора содержит предварительный инвертор с повентильной коммутацией на основных тиристорах.

l5 Предварительный инвертор собран на тиристорвх Тr Т4 и диодах pr - D4 Во Вторичной Цепи трансформатора для формирования трехступенчатой кривой включены три пары тиристоров Т,Т6) Т„- Тв Т9 - Т, о. Для достижения принудитель20 ного выключения в схеме используется узел коммутации, состоящий из двух дросселей Lr u Lq коммутирующего конденсатора С, и вспомогательных тиристоров Т,, — Т,4, диоды D, и Dg,а также вторичные обмотки коммутирующих дрос25 селей служат для сброса избыточной энергии из

517133 узла коммутации и стабилизации напряжения на С, на определенном уровне, Узел коммутации осуществляет попеременное выключение аноцной или катодной группы силовых тиристоров. Включение тиристоров Т,, Т 4 приводит к восстановлению управляющих свойств тиристоров Т1, Т„а включение тиристоров Т, „T» — к восстановлению управляющих своиств тиристоров Т2, Т4.

Устройство для управления инвертором (фиг. 2) работает следующим образом. Задающий генератор (ЗГ), регулируемый по частоте, формирует последовательность импульсов, которая поступает на пересчетную схему, представляющую собой в общем случае счетчик и дешифратор, или обычный регистр сдвига. Применительно к формированию трехступенчатой кривой напряжения пересчетная схема формирует выходные сигналы последовательно по десяти каналам 1-10, служащие как разрешающие. Последовательность импульсов от ЗГ поступает также на элемент задержки Л31, затем на регулятор длительности импульсов РГИ, на элемент задержки Л32 и на один из входов триггера Т, Выходные сигналы ЗГ, ЛЗ„РГИ, Л32 и Тприведены на фиг. 3.

Длительность задержки ЛЗ, и ЛЗ2 одинакова и должна равняться времени восстановления управляющих свойств, применяемых в силовой цепи тиристоров. Формирователи импульсов ФИ, и ФИ2 обеспечивают работу узла принудительной коммутации, подавая попеременно импульсы на тиристоры Т1< и Ti и íà Ti2 и Т,3. В первом случае это обеспечивает восстановление управляющих свойств тиристоров анодной группы предварительного инвертора, а во втором случае — тиристоров катодной группы.

Выходной сигнал с триггера Т поступает на формирователь ФИэ, подающий импульсы отпирания на тиристоры Т1 и Тэ на все время формирования нулевого напряжения, согласно кривой фор...ируемого напряжения на выходе предварительного инвертора. Схемы совпадения И вЂ” И1 о обеспечивают, согласно программе, распределение импульсов включения:«a тиристоры, находящиеся во вторичных обмотках трансформатора.

Устройство для управления инвертором содержит четыре дополнительных схемы И11, И12, И13, И14, управляемые от первой, второй, шестой, и седьмой ячеек, от импульсов, формируемых по заднему фронту РГИ, а также от датчиков тока тиристоров, находящихся на вторичной стороне трансформатора ДТ> и ДТ>. При этом сигналы от датчиков тока поступают на усилители У1 и У2, каждый из которых имеет по два выхода. Если проводит тиристор Тб, то сигнал формируется по выходу 11, если тиристор Т,, то сигнал формируется по выходу 12. Аналогично с тиристоров Т „Тв сигнал с усилителя У поступает соответственно по выходу 13 и 14.

Рассмотрим режим формирования на нагрузке первой ступени в течение времени to — t>, при этом

1б

Ю

Зь

М открыты тиристоры Т,, Т4 и Т,. Однако, если в течение времени те — t1 осуществляется возврат реактивной энергии из нагрузки в источник, то открыт тиристор Тб. При этом из датчика тока LIT> через усилитель У1 по выходу 11 на вход схемы

И,, поступает напряжение, свидетельствующее о протекании тока через тиристор Т . На входе И,, присутствует также сигнал с первой ячейки. Третий сигнал на вход схемы И,, поступает в момент t т,е. в момент окончания импульса, поступающего с

РГИ. В результате с выхода И, 1 формируется сигнал на подачу кратковременного импульса запуска на тиристор Та. Полярность напряжения на обмотках W> и W2 показана на фиг. 1. Как видно, открытие Т, приводит к восстановлению тиристора

Тб, ток нагрузки переводится на тиристор Т,. В момент времени t, происходит закорачивание первичной обмотки трансформатора предварительным инвертором, при этом нагрузка закорочена через обмотку W2 и тиристор Та. Поэтому, если реактивная энергия будет продолжать возвращаться из нагрузки в источник питания и при формировании второй ступени напряжения, а именно при включении тиристоров Т,, Т, и Т;, то потери устойчивости инвертирования не произойдет. и возврат реактивной энергии будет проходить через тиристор Tz, обмотку Wq, а не (й,) и мост обратного тока предварительного инвертора, т.е. в этoivi случае возврат будет осуществляться на том уровне напряжения на нагрузке, который должен в данное время формироваться на чагруэкс. Идентично работает схема в конце формирования;торой ступени. Если возврат реактивной энергии не закончен, то в момент времени t3 осуществляется на выходе схемы И2 формирование имчульса на включение тиристора Т; о . В этом слу: ае при не рел оде к формированию третьей ступени напряжения пг нагрузке возврат будет осуществлятьсл ца уровне напряжения третьей ступени.

Аналогично работает схема лразле пия при формировании другой полуволнь .ы:раже ая Hp нагрузке. В этом случае в момепть. вр: меии т,, и т 12 формируются импульсы на вкльэчение тиристоров Т; иТ,.

В случае, если при формировании той или иной ступени возврат реактив oh 3,èèê закончен и начинается поступление энергии ."э источника в нагрузку, формирование дополнительных импульсов HR включение тиристоров не произойдет из-за отсутствия сигналов от датчиков тока 12 входах схем совпадения.

Такое построение схемы можно распространить на любое числа формируемых ступеней на нагрузке инвертора.

Формула изоогетения

Устройство для управления однофазным тиристорным инвертором с улучшенной формой кривой выходного напряжения за счет коммутацлл вторич517133 ных обмоток трансформатора, с датчиками тока в силовой цепи, содержащее триггер, два формирователя импульсов, два элемента задержки, формирователь широких импульсов, задающий генератор, связанный через ячейки пересчетной схемы с одним извходов каждой схемы совпадения,и регулятордлительности импульсов, о т л и ч а ю ще е с я тем, что, с целью расплре ия диапазона работы инвертора на активно-индуктивную нагрузку, к выходу задающего генератора подсоединен триггер, первый фор- 1р мирователь коротких импульсов запуска тиристоров и последовательно включенные первый элемент задержки, регулятор длительности импульсов, второй элемент задержки и второй формирователь коротких импульсов запуска тиристоров, второй вход триггера подключен к выходу второго элемента задержки, а выход триггера к формирователю широких импульсов запуска тиристоров, вторые входы схем совпадения соединены с выходом регулятора длительности импульсов, а выходы схем совпадения связаны с цепями управления тиристоров, второй. выход регулятора длительности импульсов соединен со входами четырех дополнительных схем совпадения, второй вход каждой из которых соединен, соответственно, с выходами первой, второй, шестой и седьмой ячеек пересчетной схемы, а третий вход каждой из схем совпадения соединен с выходами датчиков тока в силовой цепи.

517 3."

Чэ!

ГЧ

I !

Г ) л 4

Составитель А. Придатков

Корректор Ж. Кеслер! ...,ll< гoI В. Фельдман

Тираж 874 Подписное

Ц1!1 1ИПИ Государственного комитета Совета Министров СССР по делам изобретений и открьпий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 Заказ 43, 1б2

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4