Трехвходовой дешифратор

Иллюстрации

Показать всеРеферат

ь, -с

:, ..1

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (i) 817155

К АВТОРСКОМУ СВНДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву(22) Заявлено 30.12.74(21) 2095129/26-21 (5f) Я, } .>

Н 03 К 13/24 с присоединением заявки И

Гасударственный номнтет

Свввта 1инннстров СССР ве делам изобретений и открытий (23) Приоритет(43) Опублнковано05.06.76,Бюллетень № 21 (53) УДК 681.3 .055(088.8) (45) Дата опубликования описания 20.07.77 (72) Авторы изобретения

М. М. Гаймалов и P. Ф. 1 " :арданшип

Всесоюзный научно-исследовательский институт нефте;.:;=,åëûñëîâîé геофизики (71) Заявитель (54) ТРЕХВХОДОВОЙ ДГМИФРАТОР

Изобретение.. относится к вычислительной

:технике, может использоваться в универсальных и специализированных вычислительных машинах и цифровой аппаратуре. Известен трехвходовой дешифратор, содержащий двухэмиттерные транзисторные повторители и переключатели тока, состоящие из информационного и опорного транзисторов с резисторами в эмиттерной цепи.

Цель изобретения - повышение быстродействия и надежности схемы.

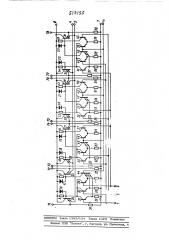

Предлагаемый дешифратор выполнен из четырех групп элементов, каждая из которых содержит два двухэмиттерных транзисторных повторителя и три информационных транзистора. Первая группа элементов содержит трехэмиттерный, а каждая из остальных — двухэмиттерный и одноэмиттерный опорные транзисторы, причем база каждого двухэмиттерного транзисторного повтори- В теля через резистор, зашунтированный диодом в прямом направлении, соединена с шиной земля, один эмиттер соединен с выходной пп ной и через резистор — с шиной питаь.. а ко "ектор соединен с шис нои "земля"„база .--,.:, .: «р::о-о трап зистора подключена . : .: .;. сь орного напряжения, а каждый эм: ..тер че :..:> резисторк шине питания; коллектор опорного транзистора первой группы соединен с базой второго двухэмиттерио«о тр., ел«горного повторителя той же груа1 !.-., колл=-кторы двухэмиттерных опорных транж сторов ВТорой, третьей и четвертой групп соединены с базами вторых двухэмиттерных транзисторных повторителей тех же групп соответственно, а коллекторы одноэмиттерных опорных транзисторов второй, третьей и четвертой групп — с базами первых двухэмнттерных транзисторных повторителей тех же групп; базы первого, второго и третьего информационных транзисторов каждой группы подключены ко входным шинам," в первой группе коллекторы всех информационных транзисторов соединены с базой первого двухэмиттерного транзиоторного повторителя той же группы, а эмиттеры — с эмитторами опорного транзистора; во второй, третьей и четвертой группах к эмиттерам двухэматтерпых опорных транзисторов подклю е.п,с эмиттеры пер517158 вого и второго, второго .и третьего, третьего и первого информационных транзисторов соответственно; коллекторы этих пар транзисторов подключены к базам первых двухэмиттерных транзисторных повторителей 5 тех же групп, коллекторы остальных информациогчых транзисторов этих групп - к базам вторых двухэмиттерных транзисторных повторителей тех же групп, а эмиттеры - к эмиттерам одноэмиттерных опорных транэис-10 торов, причем вторые эмиттеры первыхдвухэмиттерныхтранзисторных повторителей под- ключены к соответствующим управляющим шинам, На чертеже приведена принципиальная электрическая схема дешифратора.

Трехвходовый дешифратор содержит входные шины 1-3, управляющие шины 4 и 5,шину

"земля" 6,шину питания 7,резисторы 8-15,диоды 16-23,транзисторы 24-3 1 двухэмиттерных повторителей, информационные транзисторы о

32-43, опорные транзисторы 44-50, резисторы 51-70, входные шины 71-78 и шину опорного напряжения 79, причем шина

6 подключена к коллекторам транзисторов

24-31 непосредственно, а к базам — через 25 резисторы 8-15 и диоды 16-23 соответст-, венно. Шина 4 подсоединена к первым эмит» терам транзистора 25, 26, 28 и 30, шина 5 подключена к первым эмиттерам транзисторов 24, 27, 29 и 31, шина 7 подсоединена 30 через резисторы 5 1 — 58 соответственно к шинам 71 - 78, соединенным со вторыми эмиттерами соответственно транзисторов 24 - 3 1, а через резисторы 5 9- 70 — к эмиттерам сООт» ветственно транзисторов 32- 43, соединенным З5 соответственно с первым, вторым и третьим эмиттерами транзистора 44, первым и втсрым эмиттерами транзистора 45, эмиттером транзистора 46, первым и вторым эмиттерами транзистора 47, эмиттером транзистора 48, пер- 4О вым и вторым эмиттерами транзистора 49 и эмиттером транзистора 50. Шина 1 подключ на к базам транзисторов 32, 35, 40 и 42, шина

2 - базам транзисторов 33, 36, 38 и 43, а шина 79- к базам транзисторов 44- 50. Базы транзисторов 24-3 1 соединены соответствен+ .но с коллекторами транзисторов 32, 44, 35, 45, 47, 41 и 49, коллекторы транзисторов 32, 35,45,38,47,41 и49- соответственно сколлекторами транзисторов 33, 36, 3 7, 39, 40, 42 и 43, а коллекторы транзисторов 33, 36, 39 и 42 соотв" тственно с коллекторами транзисторов 34, 46, 48 и 50.

Работает дешифратор следующим образом.

Входной потенциал, превышающий потен- 55 циал шины 79, соответствует логической

"1, если же он ниже потенциала шины 79- логическому "0". При потенциале "1" иа базу одного из информационных транзисторов он отпирается, и на его коллекторе 6О устанавливается низкий уровень напряжения, который через c00TBетствуюший транзистор двухэмиттерного повторителя преобразуется в потенциал "0 на подсоединенной к его эмиттеру выходной шине. С другой стороны, на резисторе, подключенном к эмиттеру упомянутого информационного транзистора, эмиттерный ток создает падение напряжения, достаточное для эапирания связанного с этим резистором опорного транзистора по соответствующему эмиттеру. Если по остальным эмиттерам опорный транзистор также заперт, и на базах информационньи транзисторов, коллекторы которых соединены с коллектором упомянутого опорного транзистора, действуют потенциалы 0", То на этих коллекторах устанавливается высокий уровень напряжения, преобразуемый соответствующим эмиттерным повторителем в потенциал "1

Опорные транзисторы, связанные с информационными транзисторами, на базах которых действует потенциал "0", отпираются по соответствующим эмиттерам. При этом коллекторный ток отпертого опорного транзистора примерно равен сумме эмиттерньи токов через открытые эмиттерные переходы, а падение напряжения на его коллекторном резисторе мало зависит от суммарного тока, так как этУг нагруэочный резистор эашунтирован диодом, стабилизирующим нижний уровень падения напряжения на резис-, торе. Шины 4 и 5 служат для контроля исправности дешифратора, причем на шине 5 через элемент "ИЛИ, образованный вторыми эмиттерами двухэмиттерных повторителей, собираются сигналы с выходов дешифратора, соответствующих входным кодам, содержащим четное число логических "1

На шине 4 аналогичным образом вырабатывается сигнал нечетности.

Однокаскадное построение схемы дешифратора позволяет повысить его быстродействие, а упрощение связей между элементами - надежность.

Формула изобретения

Трехвходовой дешифратор, содержащий двухэмиттерные транзисторные повторители и переключатели тока, состоящие иэ информационного и опорного транзисторов с резисторами в эмиттерной цепи, о т л и— ч а ю ш и и с я тем, что, с целью повышения быстродействия и надежности, он выполнен н иэ четырех групп элементов, каждая иэ которых содержит два двухэмиттерных транзисторных повторителя и три информационных транзистора, первач группа элементов содержит трехэмиттерный, а каждая из остальных — двухэмиттерный и одноэмиттерный опорные транзисторы, причем база каждого двухэмиттерного транзисторного повторителя, через резистор, зашунтированный диодом в прямом направлении, соединена с шиной земля", один эмит- тер соединен с выходной шиной и через резистор — с шиной питания, а коллектор сое- >О динен с шиной "земля"; база каждого опорного транзистора подключена к шине опорно» го напряжения, а каждый эмиттер через резистор — к шине питания; коллектор опорного транзистора первой группы соединен с базой второго двухэмиттерного транзисторного повторителя той же группы, коллекторы двухэмиттерных опорных транзисторов второй, третьей и четвертой групп соединены с базами вторых двухэмиттерных транзисторных повторителей тех же групп соответственно, а коллекторы одноэмиттерных опорных транзисторов второй, третьей и четвертой групп соединены с базами первых двухэмиттерных транзисторных повторите- 2S лей тех же групп; базы первого, второго и третьего информационных транзисторов каждой группы подключены ко входным шинам; "в первой группе коллекторы всех информационных транзисторов соединены с базой первого двухэмиттерного транзисторного повторителя той же группы, а эмиттеры — с эмиттерами опорного транзистора; во второй, третьей и четвертой группах к эмиттерам двухэмиттерных опорных транзисторов подключены эмиттеры первого и второго, второго и третьего, третьего и первого информационных транзисторов соответственно; коллекторы этих lIBp транзисторов подключены к базам первых двухэмиттерных транзисторных повторителей тех.

:же групп, коллекторы остальных информационных транзисторов этих групп — к базам вторых двухэмиттерных транзисторных повторителей тех же групп, а эмиттеры — к эмиттерам одноэмиттерных опорных транзисторов, причем вторые эмиттеры первых двухэмиттерных транзисторных повторителей подключены к соответствующим управляющим шинам.