Коммутатор для сложных цифровых вычислительных систем

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (11)517158

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистицеских

Республик

К AOTOPCKOkhV СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено 26.09. 72(21) 1832568/26-21 с присоединением заявки № (23) Приоритет (51) М. Кл.

Н 03 К 17/02

Государственный комитет

Совета Министров СССР

IIo делам изобретений н открытий (43) Опублнковано05.06.76.бюллетень № 21 (53) УДК 621.382 (088.8) (45) Дата опубликования описания 20,07,77 (72) Авторы изобретения

P. В. 1нитько и 3, М. Черняк (71) Заявитель (54) КОММУТАТОР ДЛЯ СЛОЖНЫХ ЦИФРОВЫХ

ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении сложных цифровых вычислительных систем с большим числом процессоров, блоков памяти, входных и выходных устройств и абонентов.

Известны коммутаторы для сложных цифровых вычислительных систем, содержащие коммутационный блок и блок управления коммутацией, включающий в себя сдвигаюшие 1р регистры, выполненные на основных и вспомогательных R5 -триггерах, дешифраторы, логические схемы "И ", "ИЛИ ", «НЕ " и источник синхронизации.

Известные коммутаторы сложны, не 15 могут обслуживать абонентов при одновременном обращении их по одному и тому же адресу и имеют низкое быстродействие.

В предложенном устройстве укаэанные недостатки устранены эа счет того, что дополнительно введены двухвходовая схема

И-НЕ" и схема «И-ИЛИ-НЕ» с двухвходовыми схемами "И" по числу запрашивающих абонентов, причем одни из входов схем "И" 25 подключены к выходам соответствующих разрядов регистров, а другие — к соответствующим выходам дешифраторов, выходы которых подсоединены дополнительно к одним их входов двухвходовых схем "И« . Другие входы последних подключены к выходам соответствующих вспомогательных К В -триггеров сдвигаюших регистров, а выход дополнительной схемы «И-ИЛИ-НЕ" соединен через двухвходовую схему «И-НЕ" с синхронизирующими входами основных и вспомогательных R S -триггеров, при этом второй вход схемы "И-HE«подключен к выходу источника синхронизации.

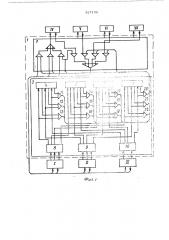

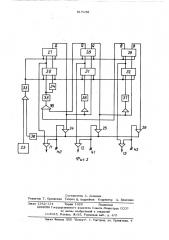

На фиг. 1 показана блок-схема предложенного коммутатора; на фиг. 2 — часть структурно-логической схемы распределителя запрашивающих абонентов.

Коммутатор 1 содержит коммутационный блок 2 и блок управления коммутацией

3, состоящий из сдвигающих регистров 4-7, дешифраторов 8, 9, 10 и логических управляющих схем «И» 11-22. Запрашивающие абоненты обозначены блоками 1, II, 111, запрашиваемые - блоками ф -ф1, 5171 58

Распределитель запрашивающих абонентов содержит источник синхронизации 23, логические схемы "И" 24, 25, 26; триггеры 27, 28, 29 с записью информации по единичному уровню синхронизируюшего напряжения; Ч э -триггеры 30, 31, 32 с записью по нулю, инверторы 33-38, логическую схему "И" 39 цля образования единицы в первом разряде регистра, когда остальные раз10 ряды равны нулю.

В исходном состоянии запросы абонентов

П, 1И равны нулю, т.е. все выходные сиг-. налы с дешифратора адреса имеют значение логического нуля. На выходе инвертора 38

15 устанавливается единичный уровень напряжения и синхрэнизируюшие импульсы Е проходят на стрэбируюшие входыЯВ- триггеров регистра, сдвигая с каждым тактом на один разряд единственйую единичку, ко20 тэрая организуется на вхоце первого разряда, когда ВсЕ остальные разряды регистра эбнулены. Нсли на эцнэм из входов 40, 41, 42 и 1II нескольких из них возникает единичный уровень напряжения, с приходом ец.лницы B сээтветствуюшем разряде

-..ключается эдна из управляющих схем "И"

11, 12, 13) и срабатывает схема блокирэвк!. синхрэнизируюших импул;- ОВ (Одна из ох=-, "И" 2 ";, 25. 26). В этом случае на выхэце инвертора 38 установится нулевой уровень и дальнейшие импульсы F в регистр проходить не будут. Такое состояние сдвигаюшегэ регистра будет сохраняться до ТВх пэр, пока единичный уровень напряжения на соответствующем выходе цешифратора обслуживаемого абонента не станет равен нулю. С обнулением указанной единички запроса импульсы Е с . . р снова проходят в сцвигаюшей регистр, и поиск запрашиваемого абонента продолжается.

Формула изобретения

Коммутатор для сложных цифровых вычислительных систем, содержаший коммутационный блок и блок управления коммутацией, содержащий сдвигавшие регистры, выполненные на основных и вспомогательных R S -триггерах, цешифраторы, логические схемы "И", "ИЛИ", "НЕ" и источник синхронизации, о т л и ч а ю ш и и с я тем, что, с целью упрощения и повышечия быстроцействия, введены дополнительно двухвходовая схема "И-НЕ" и схема "И-ИЛИНЕ" с цвухвхоцовыми схемамч "И" по числу запрашиваюших абонентов, причем одни из входов схем "И" подключены к выходам соответствующих разрядов регистров, а другие — соединены с соответстВуюшими выходами дешифраторов, выходы которых подсоединены цэполнительно к оцним из входов двухвходэвых схем "И", другие входы которых подключены к выходам соответствуюших вспомогательных 7, S -триггеров сдвигаюших регистров, а выход дополнительной схемы "И-ИЛИ-НЕ" соединен через двухвходовую схему "И-HE" с синхронизируюшими входами основных и вспомогательных А 8 -триггеров, при этом второй вход схемы "И-НЕ" подключен к выходу источника синхронизации.

5171 58

26

Составитель А. йедюхин

Редактор Т. Орловская Техред H. Андрейчук Корректор А. Власенко

Заказ 1382/134 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Заказ Филиал ППП Патент", г. Ужгород, ул. Проектная, 4