Элемент памяти с тремя устойчивыми состояниями

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i,)517162

f (61) Дополнительное к авт. свил-ву ¹ 328529 (22) Заявлено 06,01.75(21) 2093464/21 с присоединением заявки №(23) Приоритет (43) Опубликовано05.06.76.Бголлетень ¹ 21 (45) Дата опубликования описания 20.07.77 (5%) М. Кл.

Н 03 К 21/06

Н 03 К 29/00

Гасударственный номнтет

Совета Инннстров СССР оо делам изооретеннй

И PTNPblTHH (53) УД : 621 374 . 3 2(088.8 ) (72) Авторы изобретения

В, П. Грибок, Е, В. Дивин, Г, С. Анурьев и A. Ф. Косоруков (71) Заявитель (54) ЭЛЕМЕНТ ПАМЯТИ С ТРЕМЯ УСТОЙЧИВЫМИ

СОСТОЯНИЯМИ

Изобретение относится к области вычис- лительной и импульсной техники и может быть использовано как в специальных, так и в универсальных вычислительных машинах или системах. 5

Известен элемент памяти с тремя устойчивыми сос тояниями по авт. св. № 328529, недостатком которого являет» ся низкое быстродействие.

Цель изобретения — повышение быстродействия элемента.

Пель достигается тем, что выход входного элемента "И"-HE/ÈËÈ HE" каждого плеча соединен со входом выходного элемеи»

f5 та "И-HE/ÈËÈ HE последующего плеча.

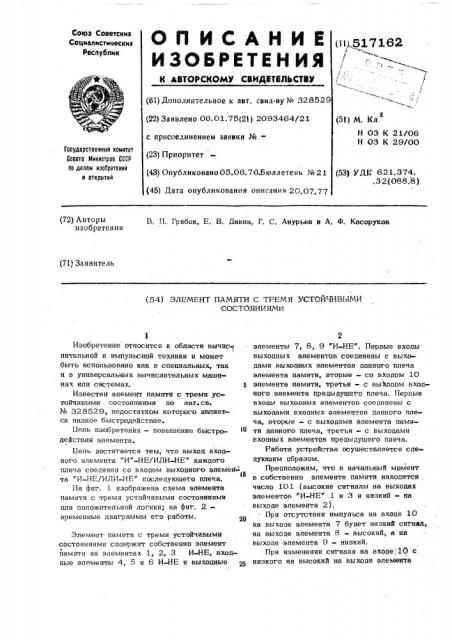

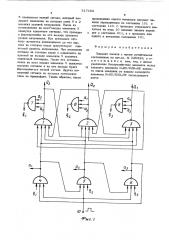

На фиг, 1 изображена схема алемента памяти с тремя устойчивыми состояниями для положительной логики; на фиг. 2временные диаграммы его работы.

Элемент памяти с тремя устойчивыми состояниями содержит собственно элемент йамяти на элементах 1, 2, 3 И-НЕ, входные алементы 4, 5 и 6 И-НЕ и выходные

2 элементы 7, 8, 9 И HE . Первые входы выходных элементов соединены с выходами выходных элементов данного плеча элемента памяти, вторые - со входом 10 элемента памяти, третьи - с выходом входного алемента предыдущего плеча. Первые входьг выходных элементов соединены с выходами входных элементов данного плеча, вторые — с выходами элемента памяти данного плеча, третьи - с выходами входных алементов предыдущего плеча.

Работа устройства осуществляется следующим образом.

Предположим, что в начальный момент в собственно элементе памяти находится. число 101 (высокие сигналы на выходах элементов "И-HE" 1 и 3 и низкий - на выходе алемента 2).

° При отсутствии импульса на входе 10 на выходе элемента 7 будет низкий сигнал на выходе элемента 8 - высокий, а на выходе -элемента 9 - низкий, При изменении сигнала на входе,10 с низкого на высокий на выходе элемента

517162

5 появляется низкий сигнал, который вызывает появление на выходах схем 9 и 2 высоких уровней напряжении. После их установления на всех входах элемента 3 окажутся единичные сигналы, что приведет к формированию на его выходе нулевого уровня напряжения. Все остальные сит налы останутся неизменными до тех пор, пока на счетном входе присутствует едичичный уровень напряжения. При изменении сигнала на счетном входе с единичного на нулевой на выходе элемента 5 появится единичный потенциал. После его установления на всех входах элемента 8 окажутся высокие сигналы и на его выходе будет формироваться низкий сигнал. Других изменений сигнала на выходах логических схем не произойдет. Таким образом, после прохождения одного импульса элемент памяти переключился из состояния 101 в состояние 110. С приходом очередного импульса на вход 10 элемент памяти перейдет в состояние 011, а с приходом еще одного в начальное положение 101.

Элемент памяти с тремя устойчивыми состояниями по авт.св. No 328529, о тличающийся тем, что,сцелью увеличения быстродействия элемента выход входного элемента И-HE/ÈËÈ HE каждого плеча соединен со входом выходного элемента И-НЕ/ИЛИ-НЕ последующего плеча

Формула изобретения о

517162 й/Х

&env

hbiu

8A od

Составитель Л. Дарьина

Редактор И. Квачадзе Техред Н. Андрейчук Корректор А. Власенко

Закаэ 1382/134 Тираж 1029 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4