Преобразователь двоично-десятичного кода в двоичный

Иллюстрации

Показать всеРеферат

Р1 517890

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советска(Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 12.12.73 (21) 1980675/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.06.76, Бюллетень № 22

Дата опубликования описания 27.07,76 (51) М. Кл.2 С 06F 5/00

Государственный комитет

Совета Министров СССР (53) УДК 681.3(088.8) по ленам изобретений и открытий (72) Авторы изобретения

А. Т. Пешков, В. А. Вишняков и Л. И. Босяков

Минский радиотехнический институт (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА

В ДВОИЧНЫЙ

Изобретение относится к вычислительной технике, где оно может быть использовано для соответствующего кодопреобразования, а также в арифметических устройствах, обеспечивающих обработку как двоичных, так и 5 двоично-десятичных операндов.

Известны преобразователи двоично-десятичного кода в двоичный (1, 2). Один из них (1) содержит динамический регистр, регистр 10 тетрады, сумматор, вентили и элемент «ИЛИ», причем выход динамического регистра соединен через вентиль и элемент «ИЛИ» со входом сумматора и через вентиль — со входом третьего разряда регистра тетрады, выходы 15 первого и третьего разрядов которого соединены через вентили со входами сумматора, а выход последнего соединен со входом динамического регистра. Это известное устройство характеризуется сложностью и значительным 20 временем преобразования. Прототипом изобретения является устройство (2), содержащее элемент переноса, регистр результата и в каждой тетрада преобразуемого числа дешифратор и сумматор-сдвигатель, к первым вхо- 25 дам которых подключен генератор тактовых сигналов. Это устройство обеспечивает преобразование и-разрядно о двоично-десятичного кода в двоичный в процессе выполнения 4и тактов сдвигов — суммирования. Однако оно 30 требует значительного времени, затрачиваемого на преобразование.

Целью изобретения является сокращение времени преобразования. В описываемом преобразогателе это достигается тем, что в нем первый выход сумматора-сдвпгателя каждой тетрады подключен к первому входу дешифратора данной тетрады, второй выход сумматора-сдвигателя каждой тетрады подключен ко второму входу соответствующего дешифратора и к третьему входу дсшифратора соседней младшей тетрады, первый, второй, третий, :,етвертый и пятый выходы дешифратора каждой тетрады, кроме тетрады единиц, подключены к первому, второму, третьему, четвертому и пятому входам сумматора — сдвигателя младшей тетрады, первый вы од дешифратора тетрады единиц подключен ко входу элемента переноса, выход которого соединен с четвертым входом соответствующего дешифратора, второй и третий выходы дешифратора тетрады единиц подключены к первому и второму входу регистра результата, выход которого соединен с выходом устройства.

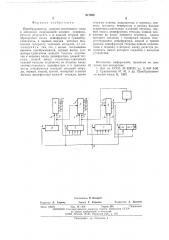

На чертеже приведена схема описываемого преобразователя для 3-разрядных (n-3) десятичных чисел. На чертеже: 1, 2 и 3 — сумматоры-сдвигатели, обеспечивающие фиксаци|о десятичных цифр исходного числа; каждый из них имеет первый вход (вход S), 517890

Таблица

Преобразованное число

M такта

Десятки

Единицы

Сотни

0111

0011

0101

0001

0000

1001

0000

0011

0011

0000 приход сигнала на который обеспечивает сдвиг содержимого сумматора-сдвигателя на два в сторону младших разрядов, первый (+2), второй (5),третий (+7), четвертый (10) и пятый (12); приход сигнала на них обеспечивает увеличение содержимого сумматорасдвигателя соответственно на два, пять, семь, десять, двенадцать; первый/ («5») и второй («2») выходы, которые соответствуют выходам второго и первого младшего разрядов сумматора-сдвигателя; 4 и 5 — дешифраторы тетрады преобразователя, кроме тетрады единиц, имеющие первый, второй и третий входы и первый (+2), второй (+5), третий (+7), четвертый (+10) и пятый (+12) выходы; 6— дешифратор тетрады единиц, имеющий первый («5»), второй («2»), третий («5») и четвертый («2») входы и а, б и в — выходы; 7— элемент переноса, являющийся ячейкой кратковременного хранения переноса; 8 — регистр результата, имеющий первый и второй входы для установки значения в первом и втором старших двоичных разрядах и третий вход, приход сигнала на который обеспечивает сдвиг содержимого регистра результата вправо на два разряда; 9 — шина генератора тактовых сигналов, подключенная к первым входам сумматоров-сдвигателей всех тетрад и к третьему входу регистра результата.

Первый выход каждого сумматора-сдвигателя соединен с первым входом дешифратора этой же тетрады, второй выход каждого сумматора-сдвигателя соединен со вторым выходом соответствующего дешифратора и с третьим входом дешифратора соседней младшей тетрады, первый (+2), второй (+5) третий (+7), четвертый (+10) и пятый (+12) выходы дешифратора каждой тетрады, кроме тетрады единиц, соединены с соответствующими входами сумматора-сдвигателя эгой же тетрады. Выход в дешифратора единиц подключен через элемент переноса к четвертому входу этого же дешифратора, выходы а и б которого соединены соответственно с первым и вторым входами регистра результата.

Особенностью дешифраторов всех тетрад, кроме тетрады единиц, является то, что их можно рассматривать как специализированные суммирующие схемы, причем, если принять для его первого, второго и третьего входов веса соответственно «2», «5», «5», то для его первого, второго, третьего, четвертого и пятого выхода будут справедливы веса соответственно «2», «5», «7», «10», «12». Особенностью дешифратора тетрады единиц (а+1) является то, что он представляет собой спе5 цнализированный сумматор, у которого входные сигналы имеют веса: первый вход «2», второй вход «1», третий вход «2», четвертый

«1», а выходы имеют веса: первый «1», второй «2», третий «4».

10 В исходном состоянии в ячейке 7 устанавливается нулевое значение, а в сумматоры-сдвигатели отдельных тетрад заносятся значения соответствующих цифр десятичного числа так, чтобы в сумматоре-сдвигателе 1 находился

15 разряд единиц, в сумматоре-сдвигателе 2 разряд десятков, в сумматоре-сдвигателе 3— старший разряд сотен. У каждого дешифратора 4 — 6 возбуждается выход, вес которого соответствует сумме весов его возбужденных

20 входов. На выходе дешифратора единиц 6 возбуждаются выходы, суммарный вес которых соответствует сумме весов его возбужденных входов.

Преобразование выполняется потактно, при25 чем каждый такт начинается с приходом сигнала на шине 9. При появлении этого сигнала обеспечивается сдвиг содержимого всех сумматоров-сдвигателей и сдвигающего регистра на два разряда вправо (в сторону младших

30 разрядов). В сумматорах-сдвигателях к коду, полученному после сдвига, прибавляется величина, соответствующая весу возбужденного выхода, подключенного к данному сумматорусдвигателю дешифратора. В сдвигающем ре55 гистре результата в освободившихся после сдвига двух старших разрядах устанавливаются значения, соответствующие сигналам на втором о и первом а выходах дешифратора 6, а в ячейке 7 устанавливается «единица», 40 если возбужден третий выход в. На этом заканчивается выполнение первого такта.

Выполнение последующих тактов происходит аналогично.

Отличием последующих тактов от первого

45 является то, что в ячейке 7 и в сдвигающем регистре результата могут находиться модульные значения.

В таблице приведена последовательность значений в разрядах отдельных сумматоров50 сдвигателей, в ячейке 7 и в двух старших разрядах rii,, т — 1 регистра результата при преобразовании числа 973за ††01111001, 517890

Формула изобретения

Составитель Н. Лакирев

Техред T. Курилко

Корректор А. Дзесова

Редактор Л. Тюрина

Заказ 1463/5 Изд. № 1414 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, >К-35, Раушская наб., д. 4/5

Типография пр, Сапунова, 2

Преобразователь двоично-десятичного кода в двоичный, содержащий элемент переноса, регистр результата и в каждой тетраде преобразуемого числа дешифратор и сумматорсдвигатель, к первым входам которых подключен генератор тактовых сигналов, отлич а ю шийся тем, что, с целью сокращения времени преобразования, первый выход сумматора-сдвигателя каждой тетрады подключен к первому входу дешифратора данной тетрады, второй выход сумматора-сдвигателя каждой тетрады подключен KO второму входу соответствующего дешифратора и к третьему входу дешифратора соседней младшей тетрады, первый, второй, третий, четвертый и пятый выходы дешифратора каждой тетрады, кроме тстрады единиц, подключены к первому, второму, третьему, четвертому и пятому входам сумматора-сдвигателя младшей тетрады, первый выход дешифратора тетрады единиц под5 ключен ко входу элемента переноса, выход которого соединен с четвертым входом соответствующего дешифратора, второй и третий выходы дешифратора тетрады единиц подключены к первому и второму входу регистра ре10 зультата, выход которого соединен с выходом устройства.

Источники информации, принятые во вни15 мание при экспертизе:

1. Авт. св. СССР, № 329525, кл. G 06F 5/00.

2. Сухомлинов М. М. и др. Преобразователи кодов чисел, К, 1965.