Устройство для цифровой индикации

Иллюстрации

Показать всеРеферат

ОП ИСАН ИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пп 517911

Соее Советски

Социалистических

Реснублии (61) Дополнительное к авт. свид-ву (22) Заявлено 03.12.73 (21) 1973859/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.06.76. Бюллетень ¹ 22

Дата опубликования описания 27.07.7б (51) М. Кл.- G 06К 15/18

Государственный комитет

Cosera Министров СССР ио делам изобретений и открытий (53) УДК 681.3.53.085.3 (088.8) (72) Автор изобретения

В. А. Скляров (71) Заявитель (54) YCTPOACTBO ДЛЯ ЦИЕРОВОй ИНДИКАЦИИ

Изобретение относится к автоматике и вычислительной технике и предназначено для вывода информации в цифровой аппаратуре.

Известны устройства для динамической цифровой индикации (1J, работающие по методу опроса индициру емых триггерных декад.

Б этих устройствах имеет место свечение нулей перед первой значащей цифрой отсчета.

Известно также ) стройство для цифровоп индикации (21, содержащее цифровые индикаторы, соединенные с дешифратором, реверсивным коммутатором и коммутирующими элементами, связанными с формирователями сигнала (регистра) запятой и с индицируемыми декадами, триггер запрета и логические схемы. Однако это известное устройство можно использовать только тогда, когда применяются индикаторы с раздельными знаками.

Целью изобретения является расширение функциональных возможностей. B описываемом устройстве это достигается введением в него дополнительного элемента «И» и элементов «ИЛИ», выходы которых подключены к дешифратору, одни входы — к выходу дополнительного элемента «И» и единичному входу триггера запрета, а другие — к выходам реверсивного коммутатора и входам дополнительного элемента «И», другой вход которого соединен с выходом триггера запрета.

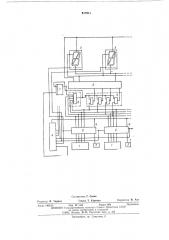

На чертеже представлена схема описываемого устройства.

Оно содержит индицируемые декады 1 и регистры 2 запятой, подключенные ко входам элементов «И» 3, входы которых подключены к соответствующим выходам реверсивного коммутатора 4 и к одним из входов индикаторов о, другие входы которых соединены с выходами дешифратора b, причем управляющий выход реверсивного коммутатора 4 соединен с нулевым входом триггера 7 запрета, а вход — с выходами элементов «И» 3, другие выходы когорых подключены ко входам дополнительного элемента «И» 8 и входами

15 элементов «ИЛИ» 9, другие входы которых соединены с. выходом дополнительного элемента «И» 8 и единичным входом триггера 7 запрета, выход — со входами дешифратора 6, а выход триггера 7 запрета соединен со входом дополнительного элемента «И» 8, элементы «ИЛИ» 9.

В исходном состоянии сигнал с выхода реверсивно o коммутатора 4 обнуляет триггер запрета 7. 11ри опросе первой и последующих

25 индицируемых декад и регистров запятой при нулевом значении кода и отсутствии сигнала запятой возникает сигнал на выходе элемента

«И» 8, и на входе дешифратора установится код «1», воспринимаемый им как запрет, Поэ30 тому нули индицироваться не будут. При на517911

Источники информации, принятые во внимание при экспертизе:

Формула изобретения 1. Авт. св, СССР № 360658, кл. G 06f 3/14, 25 1970. устроиство для цифровой индикации, содер- 2. Авт. св. СССР № 370603, кл. G 06f 3/14, жащее индицируемые декады и регистры за- 1971. личии первого не нулевого кода пропадает сигнал на выходе элемента «И» 8, что взводит триггер запрета 7 и разрешает прохождение кода на вход дешифраторов через элементы «ИЛИ» 9. После опроса декады и ре- 5 гистра запятой при наличии сигнала запятой происходит реверс коммутатора по сигналу с выхода элементов «И» 3; дальнейший опрос начинается с младшего разряда, и работа устройства происходит аналогично. 10

При опросе индицируемой декады и регистра запятой (при наличии сигнала запятой) запятая индицируется, а значение разряда— лишь в том случае, если перед этим триггер

7 был установлен в единичное состояние, т. е. 15 хотя бы один разряд был не нулевой.

В связи с тем, что значение кода анализируется до дешифрации, применение описываемого устройства возможно с любыми видами индикаторов, что расширяет его функциональ- 20 ные возможности. пятой, подключенные ко входам элементов

«И», входы которых подключены к соответствующим выходам реверсивного коммутатора и к одним из входов индикаторов, другие входы которых соединены с выходами дешифратора, причем управляющий выход реверсивного коммутатора соединен с нулевым входом триггера запрета, а вход — с выходами элементов «И», отличающиеся тем, что, с целью расширения функциональных возможностей устройства, в него введены дополнительный элемент «И» и элементы «ИЛИ», выходы которых подключены к дешифратору, одни входы — к выходу дополнительного элемента «И» и единичному входу триггера запрета, другие — к выходам реверсивного коммутатора и входам дополнительного элемента

«И», другой вход которого соединен с выходом триггера запрета.

Составитель Г. Силин

Редактор Л. Тюрина

Техред Т, Курилко

Корректор Н Аук

Заказ 1463/13 Изд. Ко. 1414 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2