Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

<и 51794l

Вевв Фоввтвкна

Сокиааистическик

Ресаублик

y 3Na i

-< iagK

g,1 МЕЛ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 05.06.73 (21) 1925643/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.06.76. Бюллетень Л 22

Дата опубликования описания 29.07.7б (51) M. Кл.2 G 11С 27/00

Государственный комитет

Совета Министров СССР аа лолам изобретений и открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

Ю. В. Кравченко и К. T. Михайлуца (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к радиоэлектронике и может быть использовано в устройствах обработки радиолокационной информации и вычислительной техники.

Известно аналоговое запоминающее устройство (1), содержащее усилитель, ключи, конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, а другая обкладка подключена,K выходу одного из ключей. Однако известное устройство 10 характеризуется наибольшими ошибками стробирования, которые определяются как четными, так и нечетными производными изменения входного сигнала. Наиболее близким из известных является аналоговое запо- 15 минающее устройство (21, содержащее усилитель, выход которого соединен с первым входом ключа, выход которого .подключен к накопительному элементу, например к одной из обкладок конденсатора, и ко входу 20 истокового повторителя, выход которого соединен с выходом устройства, вход которого подключен ко входу усилителя, второй вход ключа соединен с шиной стробирующего импульса, другая обкладка конденсатора сое- 25 динена с шиной пулевого потенциала. Однако это устройство не обеспечивает достаточной точности запоминания.

Целью изобретения является повышение точности запоминания устройства, В описы- 30 ваемом устройстве это достигается тем, что оно содержит схему стабилизации зарядного тока, вход которой соединен с выходом усилителя, а выход схемы стабилизации зарядного тока подключен ко,второму входу ключа. Кроме того, схема стабилизации зарядного тока содержит транзистор, резистор и стабилитрон, анод которого соединен с базой транзистора и через резистор — с шиной нулевого потенциала, коллектор транзистора соединен с выходом схемы стабилизации зарядного тока, вход которой соединен с эмиттером транзистора, катод стабилитрона подключен к плюсовой шине постоянного напряжения.

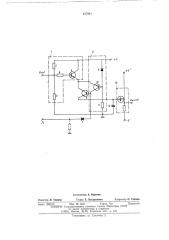

На чертеже приведена схема описываемого устройства.

Устройство содержит усилитель 1, состоящий из резисторов установки режима 2 и 3, м асштабирующего резистора 4 и тр анзистора 5, электронный ключ на транзисторе 6, диод 7, схему стабилизации зарядного тока

8, состоящую из стабилитрона 9, транзистора 10 и гасящего резистора 11, накопительный элемент — конденсатор 12 и истоковый повторитель 13.

Вход усилителя 1 соединен со входом аналогового запоминающего устройства. Выход усилителя подключен ко .входу электронного ключа на транзисторе 6, второй вход которо517941

10

3 го через диод 7 подключен к шине стробирующего импульса. Выход ключа подсоединен к одной из обкладок конденсатора 12 и входу истокового повторителя 13. Вторая обкладка койденсатора 12 подключена к щи не нулевогб"потенциала. Анод стабилитрона 9 схемы стабилизаций 8 подключен к базе транзистора 10 и через гасящий резистор

11 — к шине нулевого потенциала. Катод стабилитрона 9 подключен к плюсовой шине постоянного напряжения. Эмиттер транзистора 10 соединен с эмиттером транзистора 5 и выходом усилителя 1, а коллектор подключен к базе транзистора 6. Резисторы 2 и 3 через масштабирующий резистор 4 подключены к базе транзистора 5. Выход истокового повторителя 13 соединен с выходом аналогового запоминающего устройства.

Входной сигнал непрерывно подается на базу транзистора 5. До поступления стробирующего импульса электронный ключ на транзисторе 6 разомкнут, что обеспечивается подключением его базы к шине нулевого потенциала через открытый диод 7 и низкоомное выходное сопротивление схемы формирования стробирующих импульсов. При поступлении стробирующего импульса диод 7 запирается, транзистор 6 открывается и начинается заряд конденсатора 12.

При этом транзистор 6 выполняет уже функцию одного из элементов управляемого генератора тока.

Величина зарядного тока изменяется по закону входного сигнала, поступающего на базу транзистора 6. Стабилизация зарядного тока осуществляется поддержанием на эмиттере транзистора 5 постоянного (опорного) напряжения, которое снимается со стабилитрона 9 схемы стабилизации зарядного тока

8 и передается на транзистор 5 через составной эмиттерный повторитель, выполненный на транзисторах 6 и 10 различной структуры.

После окончания действия стробирующего импульса транзистор 6 закрывается, и на конденсаторе 12 остается напряжение, пропорциональное среднему за время выборки значению сигнала, т. е..стр.

U, = — U»(t)Ch, С где С вЂ” емкость конденсатора; асср. — .длительность стробирующего импульса;

К вЂ” масштабный коэффициент.

Нагрузкой запоминающего конденсатора является истоковый повторитель 13, выход которого является выходом запоминающего устройства.

Таким образом, аналоговое запоминающее устройство позволяет повысить точность запоминания в 1,5 — 2 раза, по сравнению с известными устроиствами, и может быть использовано в устройствах вычислительной техники.

Формула изобретения

1. Аналоговое запоминающее устройство, содержащее усилитель, выход которого соединен с первым входом ключа, выход которого подключен к накопительному элементу, например к одной из обкладок конденсатора, и ко входу истокового повторителя, выход которого соединен с выходом устройства, вход которого подключен ко входу усилителя, второй вход ключа соединен с шиной стробирующего импульса, другая обкладка конденсатора соединена с шиной нулевого потенциала, отличающееся тем, что, с целью повышения точности запоминания устройства, оно содержит схему стабилизации зарядного тока, вход которой соединен с выходом усилителя, а выход схемы стабилизации зарядного тока подключен ко второму входу ключа.

2. Устройство по п. 1, отличающееся тем, что схема стабилизации зарядного тока содержит транзистор, резистор и стабилитрон, анод которого соединен с базой транзистора и через резистор — с шиной нулевого потенциала, коллектор транзистора соединен с выходом схемы стабилизации зарядного тока, вход которой соединен с эмиттером транзистора, катод стабилитрона подключен к плюсовой шине постоянного напряжения.

Источники информации, принятые во внимание при экспертизе:

1. Бахтиаров Г. Д., Вопросы стробирования сигналов РЛС высокой точности и высокого разрешения по дальности, «Вопросы специальной радиоэлектроники», серия «Радиолокационная техника», 1969, вып. 2, с. 8.

2, Патент США М 3430072, кл. 307 †2, 1969, Редактор Л, Тюрина

Составитель А. Воронин

Техред Е. Подурушина

Корректор О. Тюрина

Заказ 1682/12 Изд. № 1437 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2