Преобразователь напряжения в код поразрядного кодирования

Иллюстрации

Показать всеРеферат

т}}т 537999

ОПИСАНИЕ

ИЗОЬЕИтИНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сок}з Советских

Соиналистических

Pec}}yáë}tê (61) Дополнительное к авт. свид-ву (22) Заявлено 10.12.73 (21) 1978058/21 (51) М, Кл.2 Н 03К 13/17 с приссед}н.ением заявки No

Государственный комитет

Совета Министров СССР на делам изобретений и отнрытнй (23) Приоритет

Опубликовано 15,06.76. Бюллетень ¹ 22

Дата опубликования описания 19.07.76 (53) УДК 681.325(088.8) (72) Авторы изобретения

А. T. Пешков и А. H. Морозевич

Минский радиотехнический институт (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ

В КОД ПОРАЗРЯДНОГО КОДИРОВАНИЯ

Изобретение относится к области вычислительной техники.

Известен преобразователь напряжения в код поразрядного кодирования, содержащий последовательно соединенные распределитель импульсов, блок вентилей, регистр, преобразователь кода в напряжение и схему сравнения, выходы которой подключены к первым входам вентилей, выход первого из которых соединен с первым входом схемы ИЛИ, а также сборку, входы которой соединены с выходами распределителя импульсов, а выход — с входом первой линии задержки и нулевым входом первого триггера, второй тр}}ггер и вторую линию задержки.

Недостатком известного преобразователя является низкое быстродействие.

Для повышения быстродействия в предлагаемый преобразователь включены дешифратор, дополнительный триггер и дополнительная схема ИЛИ, причем выходы схемы сравнения соединены с единичными входами первого и второго триггеров, своими выходами подкл}сченными к дешифратору, первый выход которого соединен с единичным входом дополнительного триггера, второй выход — с первым входом блока вентилей, второй вход которого подключен к выходу первого вентиля, и с первым входом дополнительной схемы ИЛИ, второй вход которой подключен к третьему выходу дешифратора, а выход — к первому входу распределителя импульсов, второй вход которого соединен с выходом схемы ИЛИ, второй вход схемы ИЛИ соединен с выходом второго вентиля, вторые входы вентилей подключены к выходу дополнительного триггера, третьи входы — к выходу сборки, соединенному также с нулевым входом второго триггера и второй линией задержки, выход которой подклю10 чен к нулевому входу дополнительного триггера, а выход первой линии задержки соединен с входом дешифратора.

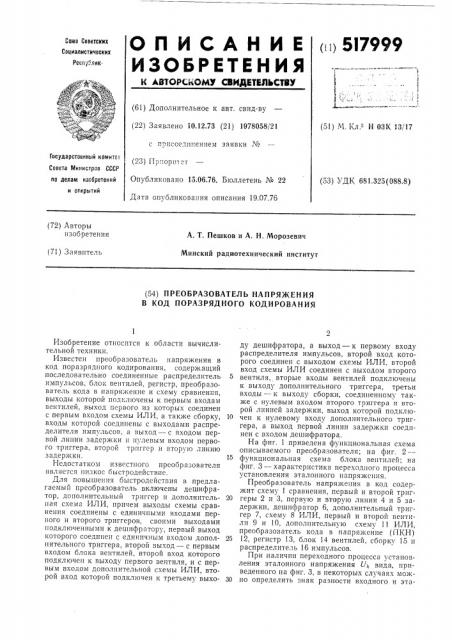

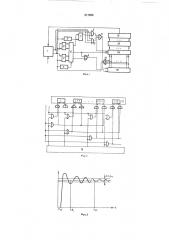

На фиг. 1 приведена функциональная схема описываемого преобразователя; »а фиг. 2-15 функциональная схема блока вентилей; на фиг. 3 — характеристика переходного процесса установления эталонного напряжения.

Преобразователь напряжения в код содержит схему 1 сравнения, первый и второй триг20 геры 2 и 3, первую и вторую линии 4 и 5 задержки, дешифратор 6, дополнительный триггер 7, схему 8 ИЛИ, первый и второй вентили 9 и 10, дополнительную схему 11 ИЛИ, преобразователь кода в напряжение (ПКН)

25 12, регистр 13, блок 14 вентилей, сборку 15 п распределитель 16 импульсов.

При наличии переходного процесса установления эталонного напряжения U}, вида, приведенного на фиг. 3, в некоторых случаях мсжЗО но определить знак разности входного и эта517999 лонного напряжений (U — Up), не дожидаясь момента 1д; конца такта уравновешивания -oro разряда, когда выполняется условие: (Uk(f ) — Uk(f„) (>boa, где А о — допустимая ошибка преобразования.

Так, если U )) Уи, то знак разности (U.„— — Ur,;) положителен; если U„«Un.;, знак разности отрицателен. Если же величина этой раз- 10 ности не превышает максимальных значений амплитуд разнополярных выбросов Ua,, величина которых зависит от величины Ua;, то величина разности становится и положительной, и отрицательной в течение такта кодирования. 15

Таким образом, если производить сравнение величин U и U> и фиксировать знаки их разности до момента времени 4; (момент времени, соответствующий максимальному выбросу в сторону, противоположную изменению UaÄ), 20 то можно в момент времени 4; прекратить анализ знака разности (U„— U>„), если знак не изменился, т. е. сократить длительность такта кодирования, или провести анализ до конца такта (4,) и перейти к анализу (i+j)ого разряда, вес которого не меньше значения максимального выброса в сторону, противоположную изменению Un; (величина выбросов может быть определена либо аналитически, либо опытным путем), т. е. сократить число З0 тактов кодирования.

Бабота преобразователя осуществляется следующим образом.

Сигнал с выхода распределителя 16 устанавливает в единицу соответствующий (i-ый) раз- 35 ряд регистра 13, с выхода ПКН 12 эталонное напряжение U>; поступает на вход схемы 1 сравнения. Сигнал с выхода распределителя через сборку 15 устанавливает триггеры 2 и 3 в нулевое состояние и опрашивает вентили 9 40 и 10. На выходах схемы сравнения в зависимости от соотношения величин U и Ug, появляются сигналы, которые устанавливают в единичное состояние либо триггер 2, либо триггер 3. Спустя время (4; — 4,) сигнал с вы- 45 хода линии 4 задержки опрашивает дешифратор 6, выходные сигналы которого определяются знаком разности (U..— Ur,;) за время (4,— 4;). Сигнал на первом выходе дешифратора появляется тогда, когда оба триггера 2 и 50

3 находятся в единичном состоянии. Сигнал с первого выхода дешифратора устанавливает триггер 7 в единичное состояние, При этом появляется сигнал на выходе одного из вентилей

9 или 10 в зависимости от состояния схемы 55 сравнения, который через схему 11 ИЛИ осуществляет переход к (+1)-ому такту кодирования. Если при этом в i-ом разряде устанавливается нуль, то все промежуточные разряды регистра с -огo по (i+j)-ый через блок 14 устанавливаются в нуль сигналом с вентиля 9 (Ux(Уи). В противном случае все промежуточные разряды регистра остаются в нулевом положении.

Если в единичное состояние переключается лишь одип из триггеров 2 или 3, то сигнал появляется соответственно либо на втором, либо на третьем выходе дешифратора. Эти сигналы через схему 8 ИЛИ осуществляют прерывание

i-ого такта распределителя и переход к (i+1)ому такту. При этом сигналом со второго выхода дешифратора (У(Уи) через блок 14 осуществляется установ в нуль i-oro разряда регистр а.

Вход 16 блока вентилей (фиг. 2) подключен к выходу вентиля 9, вход 17 — ко второму выходу дешифратора. Цепи установки разрядов регистра в единичное состояние сигналами с выходов распределителя условно не показаны.

Формула изобретения

Преобразователь напряжения в код поразрядного кодирования, содержащий последовательно соединенные распределитель импульсов, блок вентилей, регистр, преобразователь кода в напряжение и схему сравнения, выходы которой подключены к первым входам вентилей, выход первого из которых соединен с первым входом схемы ИЛИ, а также сборку, входы которой соединены с выходами распределителя импульсов, а выход — с входом первой линии задержки и нулевым входом первого триггера, второй триггер и вторую линию задержки, отличающийся тем, что, с целью повышения быстродействия, в него включены дешифратор, дополнительный триггер и дополнительная схема ИЛИ, причем выходы схемы сравнения соединены с единичными входами первого и второго триггеров, своими выходами подключеными к дешифратору, первый выход которого соединен с единичным входом дополнительного триггера, второй выход — с первым входом блока вептилей, второй вход которого подключен к выходу первого вентиля, и с первым входом дополнительной схемы ИЛИ, второй вход которой подключен к третьему выходу дешифратора, а выход — к первому входу распределителя импульсов, второй вход которого соединен с выходом схемы ИЛИ, второй вход схемы ИЛИ соединен с выходом второго вентиля, BTopbrc входы вентилей подключены к выходу дополнительного триггера, третьи входы — к выходу сборки, соединенному также с нулевым входом второго триггера и второй линией задержки, выход которой подключен к нулевому входу дополнительного триггера, а выход первой линии задержки сое",инеи с входом дешифратора.