Делитель частоты с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 518869 (61) Дополнительное к авт. свид-ву (22) Заявлено 02.12.74 (21) 2079929/21 (51) М. Кл.е

Н 03 К 23/00 с присоединением заявки №

Государственный комитет

Соввта Министров СССР по делам изобретений и открытий (23) Приоритет (43) Опубликовано 25.06.76. Бюллетень №23 (53) УДК

621.374.44 (088.8) (45) Дата опубликования описания 08.07.76 (72) Авторы изобретения

Ю. M. Ковалев и A. В. Перерушев (71) Заявитель

Специальное конструкторское бюро физического приборостро (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к радиотехнике и может быть использовано в радиотехнических установках различного назначения, в частности в системах фазовой автоподстройки систем стабилизации дискретных частот цифровых синтезаторов частоты. 5

Известен делитель частоты с переменным коэффициентом деления, содержаший последовательно соединенные источник импульсов, первый делитель частоты с первым блоком для установки коэффициента деления, первый элемент И, второй делитель 10 частоты с вторым блоком для установки, первый триггер и второй элемент И, при этом выход первого делителя частоты подключен к входам второго и третьего элементов И, выход третьего элемента И соединен с управляющим входом второго блока для 15 установки и с входом первого триггера, один из выходов которого подключен к входу первого элемента И.

Однако быстродействие известного делителя частоты ограничено временем переключения входно- 20 го сигнала с входа счетчика на вход первого делителя. Это время ограничивается возможным быстродействием выходного коммутационного узла. Коммутационный узел не позволяет получить быстродействие делителя частоты, равное быстродействию дели- 25 теля частоты с фиксированным коэффициентом деления, у которого оно максималыю возможно и о!раничивается лишь быстродействием одного функционально законченного элемента — триггера.

Целью изобретения является повышение быстродействия делителя.

Для этого в него введены второй триггер и формирователь задержки, выход которого соединен с первым управляюшим входом первого делителя частоты и с управляющим входом первого блока для установки, а вход — с выходом второго элемента И и с одним из входов второго триггера, один из выходов которого соединен с третьим входом второго элемента И и с вторым управляющим входом первого делителя частоты, а другой выход — с входом третьего элемента И, выход которого подключен к второму входу второго триггера.

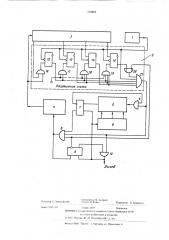

На чертеже приведена структурная элскгрпчсская схема делителя.

Делитель частоты с переменным коэффгпшснтом делсния содержит источник импульсов 1. первый делитель частоты" с первым блоком для установки 3, первый элемент И 4. второй делитель частоты

5 с BTopbIM Олоком для у становли 6. Первый триггер 7, второй элемент И 8, вгорой триггLp 9. гретий

518869

l0

1к

20 элемент И 10 и формирователь задержки 11. Первый делитель частоты включает в себя (!тФ1) — разрядный двоичный счетчик на триггерах 12 — 15 с элементами И 16-19, а также элемент.ИЛИ 20 и элемент

И 21.

Делитель частоты с переменным коэффициентом деления работает следующим образом.

В начальный момент при помощи второго блока для установки 6 во втором делителе частоты 5 устанавливается коэффициент деления Nz равный !! = ЪГ !2 где 1 оц ) — целая часть частного, Nc.u

М« — коэффициент деления первого делителя частоты и на вход первого делителя частоты 2 поступа-! ют импульсы с выхода источника импульсов 1. Первый делитель частоты 2 при этом работает в режиме постоянного коэффициента пересчета.

В качестве первого делителя частоты 2 можно использовать либо двоичный счетчик, работающий в режиме полного заполнения своих разрядов, либо двоично — десятичный, либо кольцевой или кольцевой с одной перекрестной связью. Отличие между этими счетчиками будет только в способе переключения счетчика из режима счета с коэффициентом

g „в режим счета с коэффициентом !1,= ge„+Ipse!, де Мост — т от деления Чо11щ/Мсч).

Если выбран двоичный счетчик, то его выполнение может также быть различным., синхронным, со сквозным переносом, асинхронным; важно, чтобы счетчик обладал высоким быстродействием.

Первый делитель частоты 2 выполнен в виде синхронного двоичного счетчика на триггерах 12 — 15 и элементах И 16 — 19, 21.

Коэффициент пересчета чзадается тем, что на вход элемента ИЛИ 20 с второго управляющего входа счетчика, соединенного с первым выходом второго триггера 9, подается единичный потенциал. В этом случае независимо от состояния триггера 15гт+ 1-го разряда счетчика импульс на выходе элемента И 21 появляется только в момент, когда все предшествующие й. триггеров счетчика устанавливаются в одно; например, единичное состояние.

В режиме счета с коэффициентом Йщ на выходе элемента И 16 имеется разрешающий потенциал, и триггер 12 младшего разряда счетчика работает в естественном режиме счета, т.е. изменяет свое состояние на обратное после каждого входного импульса.

При появлении сигнала на выходе второго делителя частоты 5, а он появляется с некоторой задержкой из-за более низкого быстродействия второго делителя частоты 5, срабатывает первый триггер 7. IIpv этом с второго выхода первого триггера 7 запрещающий потенциал подается на второй вход первого элемента И 4, а разрешающий потенциал с первого выхода первого триггера 7 подается на первый вход второго элемента И 8, на третьем входе которого уже имеется разрешающий потенциал с первого выхода второго ",:нггера 9.

2Ü

При оявлении на выходе первого делителя час. тоты 2 очередного импульса этот импульс поступает на второй вход третьего элемента И 10, а через второй элемент И 8 проходит на вход формирЬвателя задержки 11 и на первый вход второго триггера 9, который срабатывает по заднему фронту импульса и подает запрещающий потенциал на третий вход второго элемента И 8 и на второй управляющий вход первого делителя частоты 2. Одновременно с второго выхода второго триггера 9 разрешающий потенциал поступает на первый вход третьего элемента И 10.

Формирователь задержки 11 срабатывает по заднему фронту импульса и формирует импульс, максимальная длительность которого не должна превышать полутора периодов входных колебаний. Формирователь задержки 11 может быть выполнен либо на триггере с элементами И, на одновибраторе или в виде дифференцирующих цепочек. Импульс с выхода формирователя задержки 11 поступает на управляющий вход первого блока для установки 3 и разрешает установку во всех разрядах счетчика, кроме первого, необходимых состояний триггеров в соответствии с требуемым коэффициентом счета N< первого делителя частоты 2 в последнем цикле его работы.

Кроме того, в зависимости от того, четный или нечетный коэффициент пересчета N с одного из выходов первого блока для установки 3 на один из входов элемента И 16, либо импульс подается, либо он отсутствует. Одновременно выходной импульс формирователя задержки 11 подается на первый управляющий.вход первого делителя частоты 2. Этот управляющий вход, в случае выполнения первого делителя частоты 2 в виде двоичного счетчика, соединен с вторым входом элемента И 16.

Если коэффициент N нечетный, то на выходе элемента И 16 появляется запрещающий потенциал, который поступает на соответствующий управляющий вход первого тригге!>а и запрещает на один период входных колебаний срабатывание триггера 12 младшего разряда счетчика.

При четном коэффициент N< запрещающий потенциал на выходе элемента И 16 отсутствует и триггер 12 работает в режиме естественного счета.

При использовании предложенного способа записи коэффициента N, счетчик не может обеспечить счет с коэффициентом пересчета, равным единице, поскольку в этом случае необходимо за половину периода входных колебаний произвести установку в "единичное" состояние и первого триггера 12 счетчика.Это должно привести к снижению быстродействия ДПКД, что нежелательно. Поэтому в предложенном устройстве обеспечивается установка в первом делителе частоты 2 в последующем цикле его работы переменного коэффициента

= N. NacT =Ncq+ t 0- :(Nc„i)).

Для этой цели дополнительно введен (П+ 1)-< более старший разряд счетчика, в котором также производится установка необходимого состояния в зависимости от требуемого коэффициента пересчета К„ и выход триггера 15 (гт+1) — го разряда счетчика подключен к одному пз входов элемента И 21 через

518869 элемент ИЛИ 20, к второму входу которого подключен первый выход второго триггера 9, В начале последнего цикла работы первого делителя частоты 2 тригге 9 срабатывает и на второй вход элемента ИЛИ 20 подается нулевой потенцчал, поэтому импульс на выходе элемента И 21 появляется только в случае, когда все (n+<) триггеры счетчика установятся в соответствуюшее, например единичное состояние. Этот импульс через элемент И 10 проходит на выход ДПКД и одновременно возвращает в первоначальное исходное состояние первый 7 и второй 9 триггеры, а также поступает на управляюший вход второго блока для установки 6 и обеспечивает установку во втором делителе частоты 5 требуемого коэффициента деления hl>. При этом первый делитель частоты 2 автоматически переходит в режим работы с коэффициентом пересчета N

Формула изобретения

Делитель частоты с переменным коэффициентом деления, содержаший последовательно соединенные источник импульсов, первый делитель частоты с первым блоком для установки коэффициента деления,первый элемент И, второй делитель частоты с вторым блоком для установки, первый триггер и второй элемент И, при этом выход первого делителя частоты подключен к входам второго и третьего элементов И, выход третьего элемента И соединен с управляюшим входом второго блока для установки и с входом первого триггера, один из выходов которого !

О подключен к входу первого элемента И, о т л ич а ю ш и и с я тем, что, с целью повышения быстродействия, в него введены второй триггер и формирователь задержки, выход которого соединен с первым управляюшим входом первого делителя частоты и с управляюшим входом первого блока для установки, а вход — с выходом второго элемента И и с одним из входов второго триггера, один из выходов которого соединен с третьим входом второго элемента И н с вторым управляюшим входом первого делителя частоты, а другой выход — с входом третьего элемента И, выход которого подключен к второму входу второго триггера.

518869

Юб/ХРУ (оставитсль М. Аудринг

1 с.брсд И. Ковач

Корректор А. Гриценко

Редактор А. Зи ьковский

Заказ 3432 Зйт

Филиа I !!!l!! "Патент . г. Ужгород, ул. Проектная, 4! ираж 1039 Подписное

Ц11ИИПИ Государе венного комитета (овста Министров ГГГР по делам изобретений и открытий,113035. Москва. Ж -35. Раугнская наб.. д, 4 5