Преобразователь кодов в системе передачи и приема информации

Иллюстрации

Показать всеРеферат

О П И (Ф 1-1-И Е

ИЗОБРЕТЕНИЯ и» 519707

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 11.05.73 (21) 1916181/09 с присоединением заявки № (51) M. Кл.- G 06& 5, 02

Совета Мииистров СССР ло делам изобретений и открытий

Опубликовано 30.06.76. Бюллетень № 24

Дата опубликования описания 09.08.76 (53) УДК 621.395.345 (088.8) (72) Автор изобретения

М. Я. Эмдин (71) Заявитель

Ленинградское отделение

Центрального научно-исследовательского института связи (54) ПРЕОБРАЗОВАТЕЛЪ КОДОВ

В СИСТЕМЕ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ

Государственный комитет (23) Приоритет

Изобретение относится к устройствам автоматической коммутации различных систем и может быть использовано в городских координатных автоматичес|ких телефонных станциях (ATC) .

Известен преобразователь кодов в системе передачи и приема информации, содержащий фиксатор обрабатываемой информации, выполненный в виде четырехразрядного двоичного счетчика, информационные входы которого являются входами преобразователя кодов.

В известном преобразователе для преобразования кода «два из пяти» в двоичный код необходимо использовать дешифратор кодов, что усложняет устройство. Кроме того такой преобразователь имеет ограниченные функциональные возмож ности.

Цель изобретения — преобразование исходного кода «два из пяти» в выходной код «два из пяти», десятичное значение которото отличается от десятичного значения исходного кода «два из пяти», и расширение функциональных возможностей преобразователя.

Для этого в него введен определитель превышения четности, первые три входа кото рого соединены с тремя выходами фиксатора и счетными входами второго, третьего, четвертого разрядов счетчика, а четвертый вход — с четвертым выходом фиксатора, при этом выход определителя, превышения четности через формирователь одиночного импульса, элемент ИЛИ соединен с счетным входом первого разряда счетчика, а также введены определитель четности, входы которого соединены с выходами фиксатора, входами оп ределителя превышения четности и счетными входами разрядов счетчика, кроме первого разряда, а выход — через инвертор с избы10 точным выходом преобразователя, блок логической эквивалентности, один вход которого соединен с избыточным выходом преобразователя кодов, другой вход — с избыточным входом преобразователя кодов, а выход является выходом соответствия, и формирователь управляющих импульсов, выходы котоiporo соединены соответственно через элементы ИЛИ с прямым и с реверсивным счетными входами фиксатора, а вход подключен к

20 управляющему блоку.

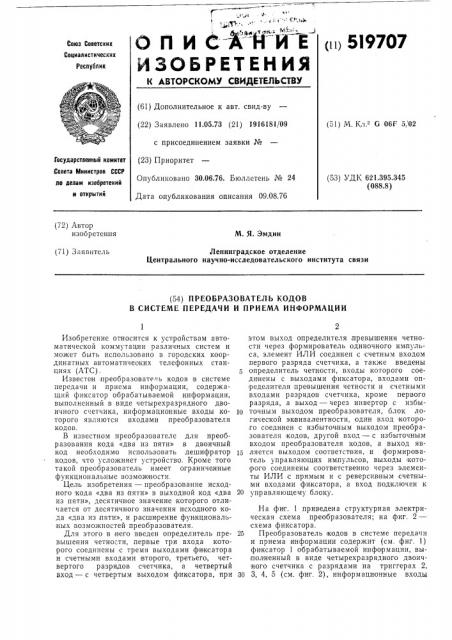

На фиг. 1 приведена структурная электрическая схема преобразователя; на фиг. 2— схема фиксатора.

25 Преобразователь |кодов в системе передачи и приема информации содержит (см. фиг. 1) фиксатор 1 обрабатываемой информации, выполненный в виде четырехразрядного двоичного счетчика с разрядами на триггерах 2, 30 3, 4, 5 (см. фиг. 2), информационные входы

519707

6, 7, 8, 9 которого яв. яются входами .преобразователя кодов, определитель 10 превышения четности, три входа 11, 12, 13 которого соединены с тремя выходами 14, 15, 16 соогветственно фиксатора 1 и счетными входами (см. фиг. 2) второго, претьего и четвертого разрядов, выполненных на триггерах 3, 4, 5 счетчика фиксатора 1, четвертый выход 17 фиксатора l соединен с четвертым входом 18 определителя 10 Кроме того, входы 1, 12, 13, 18 определителя 10 соединены с входами определителя 19 четности, выход которого через инвертор 20 подключен к избыточному (контрольному) выходу 21 преобразователя кодов, к которому также подключен один из входов блока 22 логической эквивалентности, другой вход которого подключен к избыточному (контрольному) входу 23 преобразователя, а выход блока 22 является выходом соответствия. Определитель 10 через формирователь 24 одиночного импульса, соединен с объединенными одними входами элементов И

25, И 26, выходы которых подключены к одним из входов элементов ИЛИ 27, ИЛИ 28, к другим входам которых подключены соответственно выходы 29, 30 формирователя 31

i"ïpàâëÿþùèõ импульсов. Выходы элементов

ИЛИ 27, ИЛИ 28 соединены соответственно с прямым счетным входом 32 первого разряда (триггер 2) счетчика фиксатора 1 и с реверсивным счетным входом 33 фиксатоДвоичный код

Код „два из пяти избыт. часть кода

Десятичное значение кода два нз пяти

Десятичное значение двоичного кода информационная часть кода

2о

2î

f2

При таком рассмотрении избыточный вход

23 преобразователя, которому в таблице соответст вует графа ip, не имеет никакого значения.

Таким образом, для преобразования двоичного кода в код «два из пяти» достаточно

2

4

5 б

8

1О

11

12

13

14

1

1

1

1

1

1

1

1

0

1

1

0

0

1

1

4

pa l. Другие входы элементов И 25, И 26, вход формирователя 31, информационные входы b, 7, 8, 9, избыточный вход 23, вход 33 связаны с у правляющим блоком (не показан). По входу 34 фиксатора 1 задается режим его работы.

Преобразователь кодов работает следующим образом.

Информация, предназначенная для преобразования, поступает на входы 6, 7, 8, 9 и

23 преобразователя от управляющего блока в коде «два из пяти». Информационное значение поступившей на входы 6 — 9 информации фиксируется с помощью фиксатора 1.

15 Контрольное значение поступившей по входу

23 информации вообще не фиксируется, т. е. вход 23 не используется.

Для того, чтобы лучше проиллюстрировать принцип действия преобр азов ателя кодов, 20 рассмотрим таблицу преобразования десятичного кода в двоичный код и в код «два из пяти».

Из таблицы вид но, что всем информационным значениям информации, поступившей в

25 коде «два из пяти» на входы 6, 7, 8 и 9 преобразователя (сигналы на этих входах размещены в графах f(, з, fq, fq соответственно), однозначно соответствуют определенные комбинации двоичного кода, однако десятич30 ные значения комбинаций этих кодов оказываются различными. проанализировать количество возбужденных выходов двоичного четырехразрядного счетчика фиксатора 1 и в случае, если число воз35 бужденных выходов окажется больше, чем два, на счетный вход 32 этого счетчика необходимо подать дополнительный одиночный

519707

5 импульс. Это утверждение справедливо, так как десятичному значению «7» и десятичному значению «11» двоичного кода соответствуют три возбужденных триггера двоичного счетчика.

Анализ количества возбужденных выходов четырехразрядното двоичного счетчика фиксатора 1 осуществляет определитель 10 превышения четности. При превышении четности возбужденных выходов 14, 15, 16, 17 преобразователя на выходе определителя 10 появляется сигнал, который воздействует на формирователь 24 одиночного импульса, на выходе которого появляется одиночный импульс, поступающий через элемент ИЛИ 27 на прямой счетный вход 32 счетчика фиксатора 1, в результате чего происходит преобразование информационного значения кода.

Рассмотрим пример преобразования информационных значений исходного кода «два из пяти» в выходной код «два из пяти» с др;гим десятичным значением. Предположим, что значение исходного кола «два из пяти», соответcTBvtoIIIåå десятичному значению «8», требуется преобразовать в выходной код

«два из пяти», десятичное значение которого соответствует «6». Информация о количестве шагов ппеобпазования (в данном случае два шага) вводи ся в десятичном коде в виде послеловятельных импульсов на вход элемента ИЛИ 27.

Итак. если oT .ппавляющего блока на вхочы 6, 7. 8, 9 и 23 постх"пает инФормация в коде «лва из пяти», соответствующая десятичном значению «8», то в соответствии с таблицей бх.д т переключены в рабочее состояние пепвый и четвертый пазпяды (тритгепы 2 и 51 лвоичного счетчика Фиксатопа 1.

Происходит Фиксация информационной части исхочной инфопмации. Затем под действием импульсов, поступающих на элемент ИЛИ

27. ппоисходит ппеобпазование инФовмационной части зафиксиповяннюго в Фиксаторе 1 кола «два из пяти». Под чействием пепвого импульса. постчпаюшето veDeB элемент ИЛИ

27 ня счетный вхол 32 первого пазпяда (тригleD 21 двоичного счетчика фиксатопа 1. все пязпялы pro ппинимают значения. соответстIIvIollIHe инсЬопмационной части десятичного значения «7» кода «два из пяти». В соответствии с таблицей пепвые TDH пазпяла (тпиггепы 2. 3. 41 счетчика нахочятся в исходном состоянии. à четвертый пазпяд (тпиггеп 51 — в пабочем. Пол действием втопото импульса. пот паюшето чепез элемент ИЛИ

27 ня счетный вход 32 Фиксатопа 1, все пазпялы счетчика Фиксатопа 1 ппинимают значения. соответствующие лесятичномч значе:нию «7» лвоицного кола. В соответствии с таблипей пепвые тпи пязпяда счетчика (тпигтепы 2. 3. 41 пепехолят в пабочее состояние, я четвептый пазпял (тпиггеп 51 — в исходно .

При этом оказываются возбужденными тпи инфопмационных выхода 14, 15, 16 преобпазователя, в результате чего на выходе îTlðe6 делителя 10 появляется сигнал, поступающий на вход формирователя 24, который вырабатывает одиночный импульс, поступающий через элемент «ИЛИ» 27 на вход 32 первого

5 разряда счетчика фиксатора 1. Счетчик переходит в следующее poeòoÿíHå, соответствующее десятичному значению «6» информационного значения кода «два из пяти». В соответствии с таблицей первый разряд (триг10 пер 2) счетчика возвращается в исходное состояние, второй и третий разряды (триггеры

3, 4) сохраняют рабочее состоиние, а четвертый разряд (триггер 51 — исходное. При этом на выходах 14, 15, 16, 17 появляется

15 информация, соответствующая десятичному значению «6» кода «два из пяти». Таким образом, преобразователь обеспечивает преобразование исхочного кода «два из пяти» в выхолной код «два из пяти» с чругим деся2О тичным значением. Рассмотрим .пример дополнительного использования ппеобразователя. Предположим, что двоичный четырехразрядный счетчик фиксатора 1 построен таким образом, что TIDH подаче одного имп»льса на его вход десятичное значение состояний TDHI.геров 2 — 5 счетчика уменьшается на единицч. Это значит, что, если, например, двоичный счетчик находился в состоянии «1», то ,при поступлении одного имп льва через элемент ИЛИ 27 на счетный вход 32 фиксатора 1, счетчик перейдет в исходное состояние.

Тогда, ес,чи от управляющего блока на входы 6. 7, 8, 9 и 23 преобразователя бчдет подано такое значение кода «два из пяти», десятичное значение которого соответствует «1», «2», «3», «4», «5» или «6», то двоичный счетчик вернется в исходное состояние после того, как íà BxoJI элемента ИЛИ 27 поступит один, два, TDH, четыпе, пять или шесть ими .лисов соответственно. Устпойство (не показано1, вместе с котоюым работает преобпазователь, выдает требуемое количество декадHbIX ИVIIIVJlbÑOB.

Если же от VIIDBBляющего блока на входы

6, 7. 8. 9 и 23 ппеобпазователя будет полан в коле «два из пяти» запрос на выдачх. напримеп, семи декадных импульсов, то все разряды двоичного счетчика Фиксатора 1 ппиобпет .т такое значение двоичного коча. котопом соответствует десятичное значение «8» (см. таб.лицЛ. Ппи подаче пепвого лекадного имп .льга на вход элемента ИЛИ 27 б .дет подан пепвый импульс, который поступит на вход 32 Фик ятопя 1 и пепеключит счетчик в состояние «7». Ппи этом окаж .тся возбужденными TDH пазпяда (тпиггpDbl 2, 3. 41 чвоицного счетчика Фиксатопа в пезаж.льтате чего спа ботает оппелелитель 10 ппевышения четности и подаст команд . в Жопмипователь

5О 24. На вход элемента ИЛИ 27 бчдет подан о яно ный импх льс. котопый, ностх пив на vn 32 Фиксатопя 1. пепеведет сяетчик в состояние, десятичное значение которого соответствует «6». При,поступлении:второго им55 пульса яа вход элемента ИЛИ 27 счетчик пе519707

5 !

? рейдет в состояние «5», третьего — в состояние «4», четвертого — в состояние «3», пятого — в состояние «2» шестого — в состояние

«1» и седьмого — в исходное состояние.

Таким образом, с помощью греобразователя можно обеспечить выдачу семи (для данного примера) декадных импульсов несмот|ря на то, что зафиксированное триггерами 2—

5 фиксатора 1 десятичное значение двоичного кода отличалось от десятичного значения

«7» кода «два из пяти».

В ряде случаев оказывается недостаточно иметь преобразование информационного значения кода «два из пяти», а требуется на выходе преобразователя наряду с информационным значением преобразованного кода «два из пяти» иметь его контрольное, т. е. избыточное значение.

Для преобразования в код «два из пяти» информации, зафиксированной в двоичном счетчике, достаточно проанализировать количество возбужденных выходов 14 — 17 преобразователя, и если число возбужденных выходов меньше двух, подать на контрольный, т. е. избыточный выход 21 преобразователя соответствующий сигнал. Указанный анализ состояний информационных выходов 14 — !7 преобразователя осуществляет определитель

19 четности. Если ко7и ество возбужденных информационных выходов 14 — 17 равно двум, то на избыточном выходе 21 сигнал будет отсутствовать, а если меньше двух — сигнал появится.

Рассмотрим работу преобразовате. я :".".Oâ, в котором обеспечивается проверка соответствия поступающей и зафиксированной в фиксаторе 1 информации. Этот преобразователь фиксирует информацию, приходящую из управляющего блока на входы 6. 7, 8, 9. анализирует ее с помощью определителя 19 чет ности и результат анализа выдает на избыточный выход 21. Если фиксация поступившей на входы 6, 7, 8, 9 информации в фиксаторе 1 произошла без искажения, на выхо,че соответствия блока 22 логической эквивалентности появится сигнал. Если же при фиксации имело место искажение поступившей информапии, на выходе соответствия ситнала не будет. При этом управляющий блок сможет повторно ввести в фиксатор 1 инфо рмаци1о и, если эта информация будет правильно зафиксирована, то на выходе соответствия блока 22 появится сигнал соответствия. Этот сигнал может быть реализован в управляющем блошке.

Рассмотрим работу преобразователя кодов, который обладает более широкими функциональными возможностями и предназначен для преобразования исходного кода «два из пяти» в выходной код «два из пяти», десятичное значение .которого может быть как увеличено, так и уменьшено по команде управляюгпего блока.

Двоичный счетчик фиксатора 1 выполнен для этого случая реверсивным, т, е. в-"зави8 симости от команды управляющего блока он может как суммировать поступающие на его счетный вход 32 сигналы, -.àê и вычитать их.

При появлении сигнала на выходе 29 формирователя 31 через элемент ИЛИ 27 подается на прямой счетный вход 32 фиксатора 1 сигнал, в результате чего десятичное значение поступившего из управляющего блока кода

«два из пяти» увеличивается (уменьшается) на единицу, если же на выходе 29 формирователя 31 появится и сигналоз, то десятичное значение исходного кода «два из пяти» увеличится (уменьшится) на и.

При появлении сигнала на выходе ЗО формирователя 31 через элемент ИЛИ 28 подается на реверсивный счетный вход 33 фиксатора 1 сигнал, в результате чего десятичное значение поступившего из управляющего блока кода «два из пяти» уменьшается (увеличивается) на единицу, если жс на выходе 30 формирователя 31 появится и сигналов, то десятичное зна«ение исходного кода «два из пяти» уменьшится. (увеличится) íà и.

Направление изменения зафиксированной в фиксаторе 1 информации (уменьшение или увеличение) при действии одиночного импульса на счетный вход 32 или 33 обусловлено внутренними связями ра"-.рядов (триггеров

2 — 5).

Значит в зависимости от того, какой из двух счетных входов (прямой 32 или реверсивяый 33) двоичного счетчика фиксатора 1 используется, ос, ществляется подключение к нему гыхода формирователя 24 одиночного иипульса с помощью элементов И 25, И 26, Форму 7а изобретения

Преобразователь кодов в системе переда«н и приема информации, содержащий фиксатор обрабатываемой информации, выполненный в виде етырехразрядното двоичного счетчика, информационные входы которого являются входами преобразователя кодов, отличающийся тем, что, с целью преобразования исходного кода «два из,пяти» в выходной код «два из пяти», десятичное значение которого отличается от десятичного значения исхолного кода «,чва из пяти», в него введен определитель превышения четности, первые три входа которого соединены с тремя выходами фиксатора и счетными входами второго, тРетьего, четвертого разрядов счетчика, а четвертый вход — с четвертым выходом фиксатора, при этом выход определителя превышения четности через формирователь одиночногп импульса, элемент ИЛИ соединен со счетным входом первого разряда счетчика.

2. Преобра >"..тель по п. 1, о т л и ч а юшийся тем. «то. с « 7bIo расширения функциональных возможностей, введен определитель четно ти, вхо7t.I которого соединены с выходами фиксатора, входами определителя

519707

Фиг.

Фиг.2 превышения четности и счетными входами разрядов счетчика, кроме первого разряда, а выход — через инвертор с избыточным выходом преобразователя.

3. Преобразователь по п. 2, о т л и ч а ющ ц и с я тем, что введен блок логической эквивалентности, один вход которого соединен с избыточным выходом преобразователя кодов, другой вход — с избыточным входом преобразователя кодов, а выход является выходом соответствия.

4. Преобразователь по пп. 2 и 3, о т л ич а ю шийся тем, что введен формирователь

5 управляющих импульсов, выходы которого соединены соответственно срез э,цементы

ИЛИ с прямым и с реверсивным счетными входами фиксатора, а вход почключен к управляющему блоку.