Запоминающее устройство

Иллюстрации

Показать всеРеферат

(ii) 5I976I

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт.,свид-ву (22) Заявлено 07.05.74 (21) 2024072/24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.06.76. Бюллетень Ко 24

Дата опубликования описания 09.07.76 (51) М. Кл. С 11 С 19 00 государственный комитет

Gosera Министров СССР (53) УДК 681.327.6 (088.8) по делам изобретений и открытий (72) Авторы изобретения

P. В. Смирнов и Г, Д. Софийский (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство, содержащее кольцевые сдвиговые регистры, генератор, выход которого подключен к тактовым входам запоминающих ячеек регистров и к входу счетчика, блоки записи — считывания, соединенные с разрядными шинами, и адресные шины.

Большое время обращения в таком устройстве, пропорциональное числу адресов запоминающего устройства, не позволяет использовать его в качестве оперативного запоминающего устройства цифровых вычислительных машин.

Цель изобретения — повышение быстродействия устройства.

Это достигается тем, что в устройство вве-: дены элементы «И» по количеству запоминанзщих ячеек регистров, дешифратор и сумматор. Входы сумматора подключены к выходам счетчика и адресным шинам, выходы— к входам дешифратора, а выходы дешифратора — к управляющим входам соответствующих элементов «И». Входы элементов «И» соединены с запоминающими ячейками регистров, а выходы — с соответствующими блоками записи — считывания.

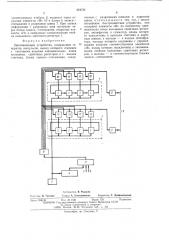

На чертеже представлена блок-схема запоминающего устройства.

Устройство содержит кольцевые сдвиговые регистры 1, состоящие из последовательно соединенных запоминающих ячеек 2, генератор 3, счетчик 4, адресные шины 5, блоки 6 записи — считывания, разрядные шины 7, дешифратор 8, сумматор 9, элементы «И» 10 по количеству ячеек 2. Входы сумматора 9 подключены к выходам счетчика 4 и шинам

5, выходы — к входам дешифратора 8, а вы10 ходы дешифратора — к управляющим входам соответствующих элементов «И» 10, входы которых соединены с ячейками 2, а выходы — с блоками 6.

Работает устройство следующим образом.

15 В случае отсутствия обращений к запоминающему устройству информация, записанная в запоминающих ячейках 2 кольцевых сдвиговых регистров 1, потактно сдвигается со скоростью, определяемой частотой работы ге20 нератора 3.

При обращении к запоминающему устройству код адреса, поступающий по шинам 5, складывается с текущим значением счетчика

4 при помощи сумматора 9. Полученный сум25 марный код адреса расшифровывается дешифратором 8. Возбужденный выход дешифратора открывает связанную с ним группу элементов «И» 10, выбирая, таким образом, слово, к которому происходит обращение. Во

30 время считывания информация, хранящаяся в

Составитель В. Рудаков

Текред А. Камышникова Корректор T. Добровольская

Редактор И. Грузова

Заказ 155б, 16 Изд. № 1430 Тира>к 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва. Ж-35, Раушская наб., д, 4/5

Типография, пр. Сапунова, 2 запоминающих ячейках 2, подается через открытые элементы «И» 10 и блоки 6 записи— считывания в разрядные шины 7. При записи информация с разрядных шин поступает через блоки записи — считывания, открытые элементы «И» в выбранные запоминающие ячейки кольцевого сдвигового регистра 1.

Фор мула изобретения

Запоминающее устройство, содержащее генератор импульсов, выход которого соединен с тактовыми входами запоминающих ячеек кольцевых сдвиговых регистров и с входом счетчика, блоки записи — считывания, соедипенные с разрядными шинами, и адресные шины, отл и ч а ю щееся тем, что, с целью повышения быстродействия устройства, оно содержит элементы «И» по количеству запоминающих ячеек кольцевых сдвиговых регистров, дешифратор и сумматор, входы которого подключены к выходам счетчика и адресным шинам, а выходы — к входам дешифратора, выходы которого соединены с управляющими входами соответствующих элементов

«И», входы которых подключены к запоминающим ячейкам кольцевых сдвиговых регистров, а выходы — к соответствующим блокам записи — считывания.