Запоминающая ячейка для регистра сдвига

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) И9763

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ

Сове Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 26.07.74 (21) 2047541/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.06.76. Бюллетень № 24

Дата опубликования описания 09.07.76 (51) М. Кл. - 6 11С 19/28

Государственный комитет

Совета Министров СССР ао делам изобретений и открытий (53) УДК 681.327.66 (088,8) (72) Авторы изобретения

Е. И. Семенович, В. А. Маленцов и П. Н. фут

"Фав (71) Заявитель (54) ЗАПОМИНАЮЩАЯ ЯЧЕЙКА ДЛЯ РЕГИСТРА СДВИГА

Изобретение относится к автоматике и вычислительной технике, в частности к запоминающим элементам цифровых устройств.

Известна запоминающая ячейка для регистра сдвига, выполненная на МДП-транзисторах и содержащая чстыре шины импульсного питания (1). Достоинство ее — малая потребляемая мощность, недостаток -- низкое быстродсй твие.

Наиболее близким техническим решением является запоминающая ячейка памяти для регистра сдвига, содержащая каскады, каждый из них состоит из зарядного МДП-транзистора, затвор которого подключен к информационному входу ячейки и к первой обкладке МДП-конденсатора, сток — к второй обкладке МДП-конденсатора и к первой шине импульсного питания, разрядного МДП-транзистора, затвор которого подключен к второй шине импульсного питания, исток — к шине нулевого потенциала, сток — к затвору зарядного МДП-транзистора последующего каскада (2). Однако такая ячейка не обеспечивает высокой надежности работы, так как при сдвиге нескольких следующих одна за другой единиц последующая логическая единица разрушает предыдущую.

Цель изобретения — повышение надежности работы ячейки.

Это достигается тем, ITQ запоминающая я-.ейка содержит в каждом каскаде разделительный МДП-транзистор, затвор и сток которого подключены к стоку и истоку зарядного МДП-транзистора соответственно, а исток разделительного МДП-транзистора — к стоку разрядного МДП-транзистора.

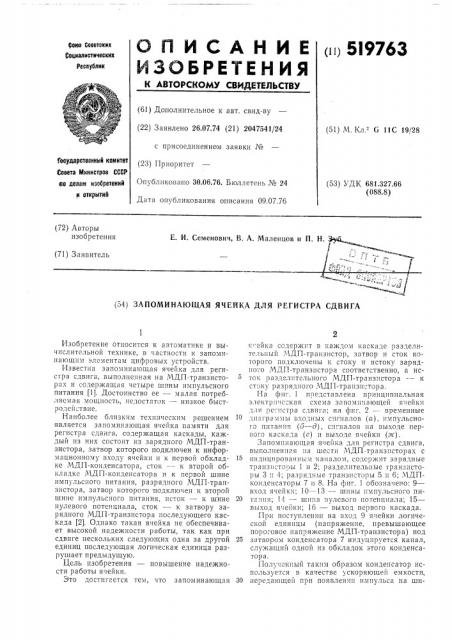

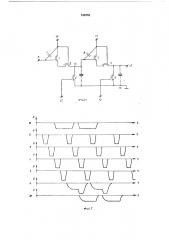

На фпг. 1 ппедставлена принципиальная электр,«:с=кая схема запоминающей я: сйки (ля,зегпстра сдвига; на фп". 2 — временные

10 диаграммы входных сигналов (а), импульсного питания (о — д), сигналов на выходе первого каска,a (e) и выходе ячейки (лг).

Запоминающая ячейка для регистра сдвига, выполненная а шести МДП-транзисторах с

15 пндицпрованным каналом, содержит зарядные трапзисто >ы 1 и 2; разделительп)яе транзисторы 3 и 4; разрядные транзисторы 5 и 6; МДПконденсаторы 7 ll 8. На фиг. 1 обозначено: 9— вход ячейки; 10 — 13 -- шины импульсного пи20 тания; 1- 1 — шина пулевого потенциала; 15— выход ячейки; 16 — выход первого каскада.

При поступлении на вход 9 ячейки логической единицы (напряжение, превышающее пороговое напряжение МДП-транзистора) под

25 затвором конденсатора 7 индуцируется канал, слу>кагций одной из обкладок этого конденсатораа.

Получснпый таким образом конденсатор используется в качестве ускоряющей емкости, ЗО передающей при появлении импульса на шине 10 импульсного питания дополнительное напряжение на затвор зарядного транзистора

1. При наличии на входе 9 логической единицы и на шине 10 импульса питания транзисторы 1 и 2 открываются и на выход 16 первого каскада ячейки передается логическая единица. После окончания действия импульса на шине 10 транзистор 2 закрывается и на емкости выхода 16 хранится логическая единица.

При поступлении импульса на шину 13 питания, разрядный транзистор 6 открывается, емкость выхода 15 ячейки разряжается на шину

14 нулевого потенциала и на выходе 15 устанавливается логический нуль (напряжение меньше порогового напряжения МДП-транзистора). С приходом импульса на шину 11 питания конденсатор 8 передает на затвор транзистора 4 дополнительное напряжение, транзисторы 4 и 5 открываются и на выход 15 передается логическая единица.

В это время на вход 9 может поступать следующая логическая единица, но так как разделительный транзистор 2 закрыт, емкость выхода 16 на шину 10 не разряжается и логическая единица передается на выход 15 ячейки. Аналогично транзистор 5 предотвращает разряд емкости выхода 15 на шину 11 при поступлении логической единицы на выход 16.

При подаче им пульса на шину 12 питания транзистор 3 открывается, емкость выхода 16 разряжается на шипу 14 и на выходе 16 устанавливается логический нуль.

Так происходит сдвиг логической единицы и подготовка ячейки к приему и сдвигу следующей информации.

При поступлении на вход 9 логического нуля конденсатор 7 имеет минимальное значение емкости (отсутствует канал под его затвором). Транзистор 1 с приходом импульса на шину 10 не открывается, и на выходе 16 сохраняется логический нуль.. Когда импульс подается на шину 13, транзистор 6 открывается и на емкости выхода 16 устанавливается логический нуль. С приходом импульса на шину 11 транзистор 4 не открывается, так как на его затворе хранится логический нуль, и на выходе 15 ячейки сохраняется логический нуль. При поступлении импульса на шину 12 открывается транзистор 3, на выходе 16 подтверждается логический нуль. Так происходят сдви." логического нуля и подготовка ячеики к приему и сдвигу следующей информации.

Наличие разделительных МДП-транзисторов выгодно отличает предлагаему запоминающую ячейку для регистра сдвига от указанного прототипа, так как снимаются ограничения, накладываемые на логические комбинации входной информации. В результате повышается надежность работы ячейки.

Формула изобретения

Запоминающая ячейка для регистра сдвига, cnдержащая каскады, каждый из которых состоит из зарядного МДП-транзистора, затвор которого подключен к информационному входу ячейки и к первой обкладке МДП-конденсатора, сток — к второй обкладке МДП-конденсатора и к первой шине импульсного питания, разрядного МДП-транзистора, затвор которого подключен к второй шине иМпульсного питания, исток — к шине нулевого потенциала, сток — к затвору зарядного МДП-транЗо зистора последующего каскада, о т л и ч а ющ а я с я тем, что, с целью повышения надежности работы ячейки, она содержит в каждом ка,-каде разделительный МДП-транзистор, затвор и сток которого подключены к стоку и истоку зарядного МДП-транзистора соответственно, а исток разделительного МДП-транзистора подключен к стоку разрядного МДПтранзистора.

40 Источники, принятые во внимание при эксIIерт; 3е.

1. США, патент 3628036, кл. 340 — 173, 1972.

2. IEEE Jornal of Solid-State С!гсшЬ vol

<; ¹ 5, 1973, р. 308- — 309.