Циклическое запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И C А- Н--И

ИЗОБРЕТЕН И

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ и 5I9764

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 21.10.74 (21) 2069374/24

1) М. Кл. - С 11С 21 00 с присоединением заявки М лсурарствеиный комитет

Cosera Министров СССР

<23) Приоритет

Опубликовано 30,06.76. Бюллетень № 24

Дата опубликования описания 09.07.76

3) УДК 681.327.6 (088.8) пл делам изобретений и открытий (72) Авторы изобретения А. В. Лисинецкий, В. Е, Баранов, А. П. Мороз и С. А. Данченко (71) Заявитель (54) ЦИКЛИЧЕСКОЕ ЗАПОМИИА1ОЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в устройствах отображения информации на экране ЭЛТ и в автоматизированных системах управления производством.

Известно запоминающее устройство (1), содержащее накопитель, выполненный на регистрах сдвига, счетчик адреса, элементы «И», дешифратор, блок управления.

Однако такое устройство не обеспечивает селективнî"o управления временем хранения информации и имеет сложную схему.

Наиболее близким из известных по технической сущности является циклическое запоминающее устройство (2), содержащее накопитель, первые входы которого соединены с блоком синхронизации, вторые входы — с входом устройства, выходы которого подключены к первым выходам накопителя, а вторые выходы накопителя — к входам дешифратора.

Недостаток известного устройства — сложность схемы.

Цель изобретения — упрощение устройства.

Это достигается тем, что в устройство введен сумматор, одни входы которого соединены с входом устройства, другие входы сумматора — с входами дешифратора. Выход дешифратора подключен к третьим входам сумматора, выходы которого подсоединены к третьим входам накопителя.

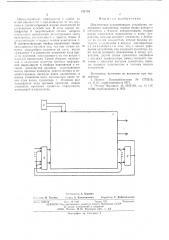

На чертеже представлена функциональная схема циклического запоминающего устройства.

Она содержит накопитель 1, блок 2 синхронизации, дешифратор 3, сумматор 4.

Принцип работы устройства заключается в следующем.

Принимаемая в произвольный промежуток времени информация записывается в накопитель 1. Одновременно в накопитель записывается код, определяющий время хранения информации, записанной в соответствующий

15 каскад накопителя. Дешифратор 3 фиксирует наличие кода в накопителе 1 и вырабатывает сигнал, поступающий на один пз входов сумматора 4 и разрешающий: в первом случае перепись информации, имеющейся в накопи20 теле, во втором — изменение кода времени хранения на число един;щ, задаваемых извне через одни входы сумматора 4. По импульсу переписи, вырабатываемому блоком 2 синхронизации, информация, содержащаяся в нако25 пителе 1, и новый код с выходов сумматора 4 записываются в первые ячейки накопителя.

На выходе накопителя записанная информация появляется вновь через промежуток времени, определяемый числом ячеек накопителя

ЗО и тактовой частотой.

Форм ул я изобретсния

Составитель A. Воронин

Техред А. Кагиь!еаникоаа

Корректор Т. Добровольская

Рсдсктор И. Грувова 4" t:;,:",1556 19 Иад.,х!е 1430 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам пвобретенпй и открытий

113035, Москва, )К-35, Раугнская наб., д. 4/5

Типография, пр. Сапунова, 2

1! и!) Ку. I, ll)OB!!i) IIC информ" !,П;1 В . Iобой Пз

H сек ПBKOi))!Tcля 1 про, 10.))жястся 10 тех нор, пока в соответствующей ячейке накопителя не у тановнтся нулевой код. Б этом случае дешифратор 3 вырябять!вает сигнал запрета

i .!1РКУг!ЯЦ!!1! Пнф0»)IBllHH;IO c:!c, IÓ!OIЦего такта пе.)сзяппсп, по.туппишсго с выходя блока 2

CI .; )(0H!lBB H!)П В HL")BL! C H HCIIKH н;! Коп!Кгеля 1.

В соответствующие ячейки накопителя также зяп;IBBIBBåòcH нул(B;)il код, !ак как сигнал за- 10 прети циркуляции подается па одни входы сумматора 4 и зяпреп;яет изменение кода вре.ме)!и хранения, поступающ г0 на его входы с

Вн)хо.t; В накопителя. Таким образом, записани I)азлH lHB!e мо>!СПTBI време;-!I; информа- 15 ция циркулирует в ячейках накопителя в теченlге п1зомсж) ткя В»смени, Определяемого кодом времени хранения, запи:ычаемым в соотзетствующие каскады ячеек накопителя, и шагом изменения кода, зад:- .Васмым извне че- 20 рез одни входы сумматора i. Изменяя шаг приращения кода времени храпения, можно управлять Врсмснсм хп Внеl п11 пи;1)орм яцип, 3 ".. II HCBH HO)1 В Н Я КОПИТСЛЬ.

Циклическое запоминающее устройство, содсржяще. накопитель, первые входы которого

c0c (I1Hспы с блоком синхронизации, вторые

В оды накопителя по:1клko÷åHû к входу устрг)й i Bя Bl:1 ;() th) KoiOрог ) соедин(:ны с пепвьl, 1! В)Я (.) :3МH ПЯ! *Ollll! ЗЛЯ, BTOPI ВЫХОДЫ KOт();,ого 1)сдк.по !ены к Входам дешифратора, Отл пч я ющееся тем, что, с цел!по упрощения уст,)ойства, оно содержит сумматор, одни входы которого подключены к входу устройства, другие входы сумматора соединены с входамп дешф)!рятора, выход которого соединен с третьпмп входами сумматора, выхо-!

IhI которого подкл!О:сны к третьим входам н" (горит ля

Источники, принятые во внимание при экспертизе:

1. Патент Великобритании ¹ 1275310, кл. 6 4С, опубликовано в 1971.

2 Гтятснт Франции № 2052140, кл. G 11С

19/00, опубликовано в 1971.