Устройство дя уравнивания частот

Иллюстрации

Показать всеРеферат

О П И С А Н И Е <„)б1цР 1

ИЗОБРЕТЕН ИЯ (61) Дополнительное к авт. свид-ву (22) 3аявленД09.09.74 (21) 2058665/07 с присоединением заявки № (23) Приоритет (51) М. Кл.

Н 02 д 3/40

Гкудврстванный иаиитат

Соната Министраа СССР иа данин) изайратаний и итирытий (43) Опубликовано 30.06.76.Бюллетень « №2 (53) УДК 621.81 6.. 729 (088.8) (45) Дата опубликования описания 11.10.76

М. Б. Вандер и А. Е. Марков

«, «qpqtaÿòp \" 1 я (71) Заявитель (54) УСТРОЙСТВО ДПЯ УРАВНИВАНИЯ ЧАСТОТ

Устройство для уравнивания частот относится к Области механики регулирования частоты синхронных генераторов и может быть использованс при синхронизации генераторов переменного тока, в частности судовых синхронных генераторов.

Известны устройства для уравнивания частот синхронных генераторов в процессе их синхронизации (lj, (2",, в которых Определение знака разности частот и формирование импульса на уравнивание частот производятся при Определенной разности фаз один раз за период разностной частоты.

l5

Ближайшим аналогом является устройство для выравнивания частот 31, содержащее блок преобразователя текущего значения разности фаз напряжений синхронизуемых генераторов в код„выходы которого О подключены ко входам цифрового решающего блока, который воздействует на регулятор скорости через формирователь выходного импульса, .Зтс vcl" ðoéñòâî реализуют жесткий алГОРп. ;.л л„)ОПОРциокальнОГО РегУ IHPGBGHHB, 25 что приводит к затягиванию процесса синхронизации, особенно при малых значениях взаимной разности частот генераторов.

Целью изобретения является повышение быстродействия системы уравнивания частот генераторов

С этой целью цифровой решающий блок содержттг блок памяти, арифметический блок вычисления приращения разности фаз, блоки сравнения этого приращения с минимальным и максимальным значениями разности фаз и блок памяти. подключенный к выходам блока преобразования, выход блока памяти подключен к входу блока вычисления приращения разности фаз, выходь>которого подключены к входам блоков сравнения текущего значения разности фаз с минимальнымизначениями этой разности и блока знака прпран;ения разности фаз, причем выход этого блока вместе с выходами блоков сравнения подключен к входам блока формирования вы» ходного импульса, второй выход которого подключен к блоку памяти.

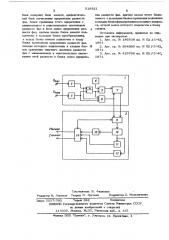

Иа чертеже представлена структурная схема ус тройства.

519821

Устройство состоит из блока преобразования 1 и цифрового решающего блока 2.

Блок преобразования включает в себя входные формировагели 3, входы которых подключены к синхронизируемым источни- 5 кам, а их выходы подключены к раздельным входам статического триггера 4-, один из выходов которого подключен ко входу схемы 5 совпадейия, на другой вход которой подключен выход генератора 6 высокочас- И чотных импульсов.

Выход схемы 5 совпадении подключен к входу счетчика 7 импульсов, установочные входы которого подключены к выходу схемы 8 запрета. Входы схемы 8 запрета подключены к выходам формирователей 3 и к выходу триггера 4. Выходы разрядов счетчика 7 и схемы 8 запрета подключены к блоку памяти 9 цифрового решающего бло-2О ка 2. Выход блока памяти 9 подключен к входу арифметического блока 10 вычисления приращения разности фаз, выходы которого, в свою очередь, поужлючены ко входу блока 11 сравнения текущего значения при- 25 ращения разности фаз с минимальным значением этой разности, ко входу блока 12 сравнения текущего значения приращения разнос ги фаз с максимальным значением этой разности и ко входу блока 13 знака ЗО приращения разности фаз. Выходы блоков

11, 12, 13 подключены к соответствующим входам блока 14 формирования импульса уравнивания частот. Выходы блока 14- подключены к регулятору скорости агрегата и 35 к входу блока памяти 9.

Устройство работает следующим образом.

Напряжения синхронизуемых генераторов

Ц и Ug s преобразуются с помощью форми 4 ай ровагелей 3 в серии прямоугольных импул 4О сов, следующих с частотой входных напряжений. Эти импульсы поступают на раздел ные входы симметричного григгера 4,,на одном из выходов которого появляются импульсы, длительность которых пропорциональ- на разности фаз входных напряжений. Импульсы разности фаз модулируюгся схемой

5 совпадения с помощью генератора 6 высокочастотных импульсов.

Модулированный сигнал поступает на Ю вход счетчика 7. Состояние счетчика 7определяется количеством импульсов заполнения за период измерения и пропорциональ но мгновенному значению разности фаз.

Параллельный код разности фаз — М,„ считывается со счетчика 7 цифровым решающим блоком 2 в моменты времени, когда

orcyrcrayer запрещающий считывание сигнал, or схемы запрета 8.

За рет на счигывмтие кода разности фаз вырабатыьаегся схемой 8 в моменты измерения этой разности при заполнении счет чика 7.

Код разности фаз Я,„запоминается в сс

oтветс»т ощей Q HeIIKQ Олока памяти 9 В следующем периоде измерения происходит аналОгичная Операция Образования кода раз ности фаз "Р. + и его запоминание в следующей ячейке памяти. После считывания и эапоминания двух следующих друг за другом значений разности фаэ напряжений генераторов блоком 10 Определяется приращение разности фаэ: ч а блоком 1 3 Определяется и запоминается знак этого приращения.

В дальнейшем приращение разности фаз в виде кода / л Y« / поступает на блоKH сравнения 1 1 к 12»В блоке 11 происходит сравнение текущего значения приращения разности фаз

/ Ь Ч « / c минимальным значением этой разности a V,..,а в блоке j 2 происходит сравнение текугцегс значения приращения разности фаз / ь V« / с максимальным значением этой разности ь Ч

В случае если текущее значение приращения разности фаз находится в пределах: а Ч .„л. л Ч „ л ь Р воздейс BBe HB регулятОр скорости не II pod» ходит.

Если же а „;, Rjgf / Клык g o g /д Дд . на блок 14 поступает сигнал рассогласования or блоков 11 или 12, после чего блок

14 вырабатывает соответствующий управляющий импуш,с на регулятор скорости. При этом воздействие происходит по одному из двух выходных каналов в зависимости or сигнала знака разности частот, поступающего на блок 14 О-. блока 13. При воздействии на регулятор скорости блок 14 одно временно воэдействуег на блок памяти 9, запрещающий считывание новой информации на период регулирования.

Формула изобретения

Устройство для уравнивания частот синхронных генераторов, содержащее блок преобразования текущего значения разнос-.и фаз напряжений синхронизируемых генерагоров в код

ВЫХОДЫ К«ОРОГО ПОДКЛЮЧЕНЫ КО ВХОДаМ цифрового решающего блока, -который воздействует иа регулятор скорости через формирователь выходного импульса, о - л и ч аю щ е е с я тем, что. с целью повышения его быстродействия, цифровой решающий

519821

fbun

Составитель К>. Филиппов

Редактор B. Левятов Техред О. Луговая Корректор а Мельниченко

Заказ 5037/592 Тираж 882 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 блок содержит блок памяти, арифметический блок вычисления приращения разности фаз, блоки сравнения этого приращения с минимальным и максимальным значениями разности фаз и блок знака приращения ра."-ьности фаз, причем входы блока памяти подключены к выходам блока преобразования, а выход блока памяти подключен к входу блока вычисления приращения разности фаз, выходы которого подключены к входам бло- 30 ков сравнения текущего значения разности фаз с минимальным и максимальным значениями этой разности и блока знака прираше6 ния разности фаз, причем выход этого блока вместе с выходами блоков сравнения подключен к входам блока формирования выходного импульса, второй выход которого подключен к блоку памяти.

Источники информации, принятые во внимание при экспертизе:

1. Авт. св. № 146838 кл. Н 02 д3/42

1961.

2. Авт. св. ¹ 394890 кл. Н 02 J 3/42

1971.

3. Авт. св. ¹ 415768 кл. Н 02 J3/40

1971.