Устройство задержки

Иллюстрации

Показать всеРеферат

II I1 539855

Союз Советских

Социалистических

Республик

k (б1) Дополнительное к авт. свид-ву (22) Заявлено 05.06.72 (21) 179i7i9/21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.06.76. Бюллетень № 24 (51) М. Кл. Н ОЗК 5/13

Государственный комитвт

Совета Министров СССР ло делам изобретений н открытий (53) УДК 621.374.5 (088.8) Дага опубликования описания 27.07.70 (72) Авторы изобретения

В. П. Бакалинский н А. Г. Хлонь (71) Заявитель (54) УСТРОЙСТВО ЗАДЕРЖКИ

Изобретение относится к радиотехнике и может быть использовано для формирования временных интервалов повышенной стабильности.

Известно устройство задержки, содержащее симметричный триггер с раздельными входами, с подключенной к его выходам времязадающей RC-цепью, параллельно которой подключен переменный резистор, диодно-регенеративный компаратор с двумя диодными входами, выход которого через диод соединен с одним из выходов симметричного триггера с раздельными входами.

Цель изобретения — увеличение времени задержки импульсов напряжения.

Для этого в предлагаемом устройстве один из диодных входов диодно-регенеративного компаратора подключен к точке соединения резистора с конденсатором времязадающей

RC-цепи, а другой диодный вход диодно-регенеративного компаратора подкл?очен к подвижному контакту переменного резистора.

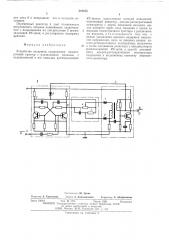

На чертеже приведена принципиальная электрическая схема предлагаемого устройства задержки.

Устройство задержки содер>кит симметричный триггер 1 с раздельными входами,. Между выходами триггера 1 включена времязадающая RC-цепь, состоящая из резистора 2 и конденсатора 3, параллельно которой подключен переменнь:и резистор 4.

Ди gi?IO-pCI eirep3THBHbiil KOillri3p3TOp 5

II!iceT два диодных входа. Диод б подключен к то ке соедп Icния резистора 2 с конденсатором 3, а диод 7 соединен с подви>кным контактом переменного резистора 4. Выход диоднорегенеративного компаратора 5 через диод 8 сседннеп с одним из выходов триггера 1.

10 Устройство задер>кки работает следующим ооразом.

В исходном состоянии симметричный триггер 1 находится в таком состоянии, что напряжение на его выходе 9 по абсолютному

15 значению больше, .чем напряжение на выходе 10. Конденсатор 3 времязадающей RC-це-!

?н заря>ксп ?Io разности этих напряжении.

11рн поступлении на вход 11 триггера 1 запускающего импульса трш«гер 1 меняет свое

20 состояние. Напряжение на его выходе 9 по абсолютному значению становится меньше, чем напряжение на его выходе 10. Конденсатор 3 времязадающей RC-цепи начинает перезаряжаться до разности этих напряжений.

В момент сравнения напряжений на конденсаторе 3 времязадающей RC-цепи н на переменном резисторе 4 срабатывает компаратор

5, выдавая одиночный импульс на выходе 12.

ЗО Зтот импульс подается па вход триггера 1 через диод 8 и возвращает его в исходное состояние, Переменный резистор 4 дает возможность регулировать опорное напряжение, сравниваемое с напряжением на конденсаторе 3 времязадающей RC-цепи, и регулировать выдержку времени.

Формула изобретения

Устройство задержки, содержа1цее симметричный триггер с раздельными входами, с подключенной к его выходам времязадающей

RC-цепью, параллельно которой подключен перемснный резистор, диодно-регенеративный компаратор с двумя диодными входами, выход которого через диод соединен с одним нз

5 выходов симметричного триггера с раздельнымн входами, отличающееся тем, что, с целью увеличения времени задержки импульсов напряжения, один из диодных входов диодно-регенеративного компаратора подключен

10 к точке соединения резистора с конденсатором времязадающей RC-цепи, а другой диодный вход диодно-регенеративного компаратора подключен к подвижному контакту переменного резистора.

Состагитслв Ю. Еркин

Редактор Е. Караулова Тскред A. Камышникова Корректор А. Абдряхимова

Заказ 1562,9 Изд. № 1175 Тираж !029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, )I(-35, Раушская иаб., д. 4, 5

Типография, пр. Сапунова, 2