Преобразователь двоичного кода в десятичный

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (11) 52() (б1) Дополнительное к авт. свид-ву (22} Заявлено 10.06.74 (21) 2033487/24 с присоединением заявки № (23) Приоритет(43) Опубликовано 05.07.76.Бюллетень № 25 (46} Дата опубликования описания 29.09.76 (51) М. Хл.е

G 06 F 5/02

Гасударственный нватет

Савла Мнннетрав СССР ва делен нвааретеннй н атнрьпнй (53) УДК 681.325 (088.8) (72) Авторы изобоетення

В. А. Вишняков и А. Т. Пешков (71) Заявитель

Минский радиотехнический институт (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В

ДЕСЯТИЧНЫЙ

Изобретение относится к области вычислительной техники и может быть использовано в ус".ройствах информапни двоичной вычислительной иаши;.-, Известен преобразователь двоичного кода в десятичный, содержащий набор тетрад по числу разрядов десятичного кода, каждая из которых содержит четырехразрядный регистр сдвига и дешифратор.

Недостатком известного устройства явля- 10 ется невысокое быстродействие.

Белью изобретения является повьпнение быстродействия.

Эта цель достигается эа счет того, что в пре:;::,.оженном преобразователе в каждой д тетра..,-.-. первые управляющие входы дешифрато х: — .3 четырехразрядчого регистра сдви га соед. ч;н ы и подключены к первой входной шине, первый, второй и третий выходы дешифратапа соединены со входами первого, 20 второ::о и третьего разрядов регистра сдвита„ въ:.;одь< всех разрядов которого соединены с;:: тветствуюшнми информапионными входами дешифратора, второй управляющий вход ко" :;.îãà соединен счетвертым выходом 25 дешифратора предыдущей тетрады. Пятый вы ход дешифратора соединен со вторым управляющим входом четырехразрядного регистра сдвига последующей тетрады, а шестой - с третьим управляюшим входом четырехразрядного регистра сдвига ой же тетрады.

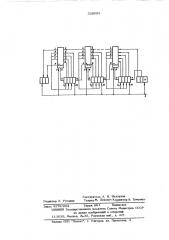

Структурная схема предлагаемого устройства для тт -разрядных десятичных чисел приведена на чертеже, где обозначены: четырехразрядные регистры 1 — 1 сдвига тетрад, имеющие первый управляющий вход тп, на который подается тактирующий сигнал, второй управляющий вход и, поступление сигнала на который обеспечивает установку значения в младшем (четвертом) разряде регистра сдвига, третий управляющий вход, сигнал на котором разрешает сдвиг„, содержимого тетрады на два разряда в.сторону младших разрядов„выходы первогo, вторol" 0, третьего .- четвертого разрядов, а также входы г .рвогo, второго и третьего разрядов: и .шифраторы тетрад 2 (т + } (2л + > каждый из которых имеет первый управляющий axon P, на который поступает тактирующий сигнал, второй управляюший вход 8, ыоззз

Таблица 1

О О 1 1 О

О 1 О 0 О

0 О l 1 0

0 1 1 1 О четыре информационных входа G, Ь, с и Я, подключенные к соответствующим выходам разрядов регистра сдвига этой же тетрады, первый А второй В и третий С выходы, подключенные к первому, второму и третьему входам четырехразрядного регистра сдвига этой же тетрапы, четвертый выход, подключенный ко второму управляющему входу дешифратора соседней слева (старшей) тетрады, пятый выход, подключенный ко второму управляющему входу регистра сдвига соседней слева тетрады, и шестой выход, подключенный к третьему управляющему входу регистра сдвига этойже тетрады; первая вход ная шина 3, подключенная к первым входамде15 шифраторов и четырехразрядных регистров сдвига всех тетрад, по которой подается тактирующий сигнал и регистр 4 исходного двоичного кода.

Устройство работает следующим образом.

В исходном состоянии во всех разрядах регистров сдвига тетрад устанавливае1 ся нулевой код, в регистре d - преобразуе» мый двоичный код. Преобразователь работает потактно по сигналам шины и выпол25 няет полное преобразование за М/2 тактов (где М вЂ” разрядность исходного двоичного числа).

В каждом такте в зависимости от сигналов на входах 8, О., Ъ, с, d, дешифраторы

30 на своих выходах по сигналу на входе P вырабатывают или сигнал разрешения сдвига на два разряда (сигнал на выходе К), или сигналы на выходах АВ,,С для установки

Э 1

35 соответствующего кода в трех старших ра=-ьрядах регистра той же тетрады. Кроме этого, дешифраторы вырабатывают на своих выходах сигналы переноса в соседнюю старшую тетраду (сигнал переноса "2» на выходе L и сигнал переноса 1 на выходе Я ).

Выработка сигналов на выходе дешифра-ара в зависимости от сигналов на его входах производится следующим образом. Если в регистре данной тетрады зафиксированы коды 0000, 0001, 0010 и в последнем случае нет переноса 2" из соседней младшеи тетрады, то в данной тетраде разрешается сдвиг кода регистра на два разряда влево по сигналу на выходе К дешифратора.

Если в тетраде зафиксированы коды 0011, 0100, 01 01, 0110, Olll, 1000, 1001, то запрещается сдвиг в данной тетраде и происходит коррек:пия кода последней и формируются переносы в старшую тетраду. 3апрет сдвига и коррекция кода регистра данной тетрады выполняет я и тогда, когда на момент начала такта в регистре зафиксирован код 0010 и в данную тетраду приходит перенос 2 (сигнал на выходе дешифратора) из младшей тетрады.

В таблице 1 представлены выходные сигналы, формируемые дешифратором тетрады при разлитых комбинациях сигналов на его вхо де. При этом перенос "1 образуется при пьредаче десятка из данного десятичного разряда в старшей, перенос 2 образуется при передаче двух десятков, при передаче трех десятков из данного десятичного разряда образуются одновременно перенос 2 и перенос 1 в следующий разряд (сигналы с выходов1и М дешифратора данной тетрады, поступающие в соседшою старшую тетраду)

При коррекции младший разряд регистра тетрады устанавливается в соответствующее состояние парафажым сигналом Я, поступающим из соседней тетрады.

На основании приведенной таблицы можно составить следующие функции зависимости выходов дешифратора входных сигналов

A--аде чреде v ъс de в = а.-ае ааа v e-дечаЬде асД

C = <е Ч ЬСде Y де Y 66 V3cd6

L =О. М88v50

5 =Ь май Vcde

Для более наглядной иллюстрации работы преобразователя в таблице 2 приведены промежуточные значения в тетрадах преобразователя на отдельных тактах преобразования двоичного кода 101011011001, 2 7 7 7

Таким образом после выполнения шести тактов бутет преобразовано двенадцатиразрядное двоичное число.

520583

Продолжение табл. 1

Таблица 2

Формула изобретения йреобразователь двоичного кода в десятичный, содержащий набор тетрад по числу разрядов десятичного кода, каждая из которых содержит четырехразрядный регистр g) сдвига и дешифратор, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия, в каждой тетраде первые управ ляющие входы дешифратора и четырехра=- рядового регистра сдвига соединены и под- 55 ключены к первой входной шине, первый, второй и третий выходы дешифратора соедииены со входами первого, второго и третьего разрядов регистра сдвига, выходы всех разрядов которого соединены с соответствующими информационными входами дешифратора, вторй управляющий вход которого соединен с четвертым выходом дешифратора предыдущей те:",зады; пятый выход дешифрагора соединен со вторым управляющим входом четырехразрядного регистра сдвига последующей тетрады; шестой выход дешифратора соединен с третьим управляющим входом четырехразрядного регистра сдвига той же тетрады.

520583

Составитель А. И. Шкатулла

Редактор Л. Утехина Техред М. Ликович КорректорА. Гриценко

Заказ 4379/204 Тираж 864 Подпис ное

UHHHIIH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4