Логическая запоминающая ячейка

Иллюстрации

Показать всеРеферат

Gll HCAHHK

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскмн

Соцмалмстн4есимн

Республик (11)520586 (61) Дополнительное к авт. свид-ву(22) Заявлено 02.07.74(21) 2040760/24 с присоединением заявки Зф (23) Приоритет (43) Опубликовано 05.07.76Бвллетень % 25 (51) М. Кл,в

G 06 F 7/00

Государственный комитет

Совета Министров СССР

IIo делам нзооретеннй н открытий (53) УДК 6Â1.326, (088.8} (45) Дата опубликования описання03.09.7ф

E. П. Балашов, N. С. Куприянов, и Г. А, Петров (72) Авторы. изобретения р

j д

Ленкнграаскнр орлана Ленина алектротекннкескир инс иттт - r

1 „ им. В, И. Ульянова (Ленина)

) Ч рр gj (71) Заявитель

{54} ПОГИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА

Изобретение относится к области вычйспитепьной техники и может быть испопьзовано при построении ассоциативных запоминаюших устройств и средств обработки информацли, обладеюших ьысокой регулярностью и функциональной гибкостью.

Известна логическая запо.пинающая ячейка, содержащая элемент памяти, четыре двухвходовых элемента И, шину считывания оперативной информации, две шины считывания постоянной информации, две разряд-; ные шины, к каждой из которых подключен эпемент памяти двух элементов И", первые входы которых соединены со входами управления ячейки соответственно, а вторые д входы объединены попарно и подключены соответственно к прямому и инверсному

„входам ячеики..

В известной логической запоминающей зО

:ячейке логические операции осуществляются только меж@" входной переменной и опе-, ративной информацией, представляющей собой состояние эпемента памяти, цепь изобретения — расширение функци- 25

I опальных возможностей логической запоминающей ячейки, Эта цепь достигается тем, что в логическую запоминающую ячейку введены два элемента задержки и два дополнительных двухвходовых элемента И", первые входы которых подключены к соответствующим входам управления ячейки, а вторые - к соответствующим разрядным шинам. Выходы дополнительных элементов И подкпючены через соответствующие элементы задержки к прямому и инверсному чходам ячейки соответственно.

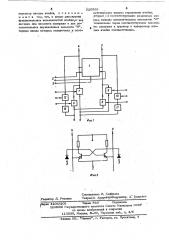

На фиг. 1 изображена погическая запо минаюшая ячейка; на фиг. 2 - принципиальная схема элемента памяти со скрытым изображением .

Логическая запоминающая ячейка содержит элемент памяти 1 со скрытым изображением, предста пяюи:ий собой триг

rep с раздельными. входами на биполярных транзисторах, ши „у считывания оперативной информации 2, две шины считывания постоянной информации 3, рве разряд ые шины 4 и 5, к каждой пз которых. подклю520586 и чен элемент памяти 1 и выходы двух элементов «И«6, "И 7 и "И"8, «И" 9, первые входы которых соединены со клодами управпеньл ячейки соответственно, а вторые входы объединены попарно и подключены соответственно к прямому и инверсному входам ячейки. В логическую запоминающую ячейку введены два элемента задержки 10, 11 и д а дополнительных двухвходовых элементе "И 12, первые входы которых подключены к соответствующим вхо» дам управления ячейки, а вторые - к соответствующим разрядным шинам 4,5. Выходы элементов И 1, 13 подключены через соответствующие элементы задержки 10, 11 к прямому и инверсному входам ячейки со. ответственно.

"Скрытое изображение> создается подключением диода (элемента И") к .плечу триггера. Лри подключенйи к одному плечу триггера он!создает скрытую 1", к другому - скрытый 0 . При подключении двух

: . диодов (как показано на фиг. 2) можно xpa нить в элементе памяти скрытый О и

"скрытую 1".

Для считывания оперативной информации на шину 2 подается сигнал, который обу.славливает появление другого сигнала либо на шине 4, либо на шине 5 в зависимости! от хранимой информации. При записи новой информации сигнал подается одновременно не шину 2 и на одну из шин 4 ипи 5. При считывании постоянной информации сигнал подается одновременно на шину 2 и одну. из шин 3.

Реализация погичес1;их операций между входной переменной и, оперативной i информацией происходит при подаче управляющих сигнапов на элементы "И"6 — 9 и сигнала на шину 2. Вид логической операции определяется набором управляющих сигналов.

Обозначим через двоичные переменные:

- состояние элемента цамяти, Sg - сиг, нал на единичном, а S — сигнал на нулевом входе элемента памяти, появляющиеся на разрядных шинах при реализации логи. . ческих операций, Z - сигнал на прямом выходе элемента памяти (прямой разрядной шине), Й » сигнал на инверсном выходе элемента памяти (инверсной разрядной шине), f — управляющий сигнал (à — номер элемента И", на который подан AGE»

"р ный управляющий сигнал) > Х> Х прямое . и инверсное, значения!входйой йеременной.

Йпя триггера с дублированными переходами функция переходов запишется: (((4 3) = (Ь ф (82 ф1 б) а входные сигналы 5 (Ц и S>(t)опредепяются выражениями

s,(11= (х x vxg„) ), (2! а «)=t-< f 1

Подставляя выражения (2)и (3) в выражение (1) и полагая ф() = P(9(t)), после соответствующих преобразований получим: ((-+ )) >

= f (g,чх,) 9(v) v (х, ч х,) (ц)3

M ц

Таким образом, подавая определенный набор управляющих сигналов на элементы

"И"6-"И 9, можно реализовать любую из шестнадцати лог ;ческих функций. Например, 5 при подаче управляющего сигнала только иа элемент И 6 реализуется логическая операция ИЛИ«, при подаче управляющих сигналов на логич>.ские эпементы «И«7, "И "8- погическая операция «инверсия Х", Й© При реализации погических операций между опера"ивной и постоянноч информациями запоминающая ячейка работает в два такта.

В первом тахте происходит считывание постоянной информации при подаче сигналов

М на шину 2 в одну из шин 3. В этом:же так-; те подаются управляю хие сигналы на эпементы "И 12, 13, благодаря чему считанная информация с разрядных шин 4 и 5 поступает на элементы задержки 16, 11, Э@ Во втором такте через время, определяемое элементом задержки, подаются управляющие на элементы "И 6- И 9 к сигнал на шипу 2. В результате реализуется логическая операции между постоянной и опера тивной информациями, определяемая также выражением (4), в котором в качестве прямого и инверсного значений Х выступают прямое и инверсное значения считанной постоянной информации.: р Таким образом, изсоретение имеет рас- . ширенные функциональные возможности, заключающиеся в реализации логических операций между оперативной и постоянной:ин формацией, хранящейся в элементе памяти со скрытым изображением. формула изобретения о щ Логическая запоминающая ячейка, со держащая элементы пе ляти, четыре двухвходовых элемента "И, шину считывания оперативной информации, две шины считывания постоянной информации, две разряд-!!р ные шины, к каждой из которых подключен элемент памяти и выходы двух "„мтементов 1

И, первые входы которых соединены со входами управления ячейки соответственно, а вторые входы объединены попарно и под

@y ключены соответственно к прямому и инСоставитель И, Сейфулла

Техред Н, АндрейчукКорректор; A. Грицейко

Редактор Л. Утехина! Закж 4206/205 тираж 863 Подписное

GhHHIIH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5 Филиал ПП »Патент, г. Ужгород, ул. Проектная, 4 версному входам ячейки, о т л и ч а юш а я с я тем, что, с целью расширении функциональных возможностей ячейки,в нее введены два элемента задержки и два дополнителыых двухвходовых элемента И, первые входы которых подключены к соот520586 6 ветствуюшим входам управления ячейки, ;вторые — к соответствующим разрядным ши нам; выходы дополнительных элементов "И» подключены через соответствующие элемен-! ты задержки к прямому и инверсному вхо. дам ячейки соответственно..