Делитель с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (»)520689 (61) Дополнительное к авт, свид-ву— (22) Заявлено 17.01.75 (21) 2096836/26-21 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано05 07 76,Бюллетень ¹25 (45) Дата опубликования описания 08.12.76 т (51) М. Кл.

Н 03 К 22 24

Государственный комитет

Совета Министров СССР оо делам иэооретений и открытий (53) УДК 681.374. .44 (088.8) (72) Автор изобретения

A. В. Шанин (71) Заявитель (54) ДЕЛИТЕЛЬ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ

ДЕЛЕНИЯ

tl чар д

Настоящее изобретение предназначено для систем, синхронизации, управляемых цифровыми вычислительными устройствами.

Известны делители частоты, используемые для построения цифровых синтезаторов частоты и систем синхронизации (1, 2).

Первое из известных устройств содержит счетчик импульсов на триггерах, выходы каждого из которых соединены с разрядными входами дешифратора скважности, дру- щ гие разрядные входы управления которого соединены с выходами блока управления, а точки соединения вхоцов дешифратора скважности с триггерными разрядными входами и разрядными входами управления соединены 1к со входами дополнительного дешифратора, выходы которого подключены к дополнительному триггеру.

Второе из известных устройств — делитель с переменным коэффициентом деления 20 — содержит двухтакгный двоичный счетчик, состоящий из информационного и буферного регистров и вентилей переноса на входе информационного регистра, вентили ввода и элемент совпадения. 25

Однако в этом устройстве ввод поправки и формирование выходного сигнала происходят в момент перехода двоичного счетчика т) 11 из состояния 2 — 1 в состояние 2 (т1—

-число разрядов двоичного счетчика), При этом. управляющее числой „представляет собой дополнительный код коэффициента деления К д, т.е.

Код, вводимый непосредственно. в двоичный счетчик (код поправки — N ), также равп няется Н = 2 — Кд, т.е. представляет собой дополнительный код коэффициента деления.

Такой характер управления сменой коэффициента деления не позволяет использовать для управления, целителем. непосредственно прямой код коэффициента деления, Это существенно ограничивает возможности применения,целителей с переменным коэффициентом деления при построении систем синхронизации, работающих в автоматическом режиме управления от ЦВУ, так как требует, 520689 я,;. а-: -,-.;::"..=.ïoëíèòåëüíûé код коэффициента делени:;:, Цель изобретения — расширение функциональных возможностей делителя.

Предлагаемый делитель отличается тем., что в него введены элемент ИЛИ и инвертор, вход которого соединен с выходом. первого вентиля ввода, а выход — с. установочным входом первого триггера информационного регистра, причем выходы остальных 1О вентилей ввода подключены соответственно к установочным входам остальных триггеров информационного регистра, входы элемента совпадения соединены с выходами триггеров буферного регистра, а его выход подключен l5 ко входам. вентилей ввода, ко входу последнего вентиля переноса и к первому входуэлемента ИЛИ, другой вход которого соединен с выходом первого триггера буферного регистра, а выход — со входом первого венти-> ля переносe.

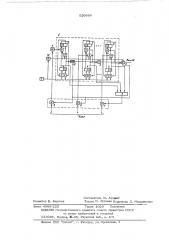

На чертеже представлена структурнаясхеiv! 8,де а:.: еля с пе ре.":=.ньь1м коэффициентом деления, Делитель содержит генератор эталонных г-cQB, дв, ..",:-хтный двоичнь|й счетчик

2, состоящий из информационных 3 и буферньх 4 регистров::,: вентилей переноса 5, вент::-:гл ввода 6, инвертор 7, элемент ИЛИ 8, элемент совпадения 9 на входов и фа,зовращатель 10 ь.=.

Работает устрой=.т- следунщим.образом. каждый импульс частоты т.. с генератора

1 переписывает к.- д и:,-формационного регистра 3 в буферный регистр 4 и, пройдя через фазоврашатель 10, увеличивает код информационного регистра 3 на единицу.

После того как двухтактнь|й двоичный счетчик 2 сосчитал (2" — 2) импульсов

1 т, . в информационном регистре 3 уста40 и навливается код 2" — 2, т.е. его первый разряд имеет состояние "0", à все его старшие разрядьг — состояние "l". 2 — 1-вый им— пульс т переписывает код 2 — 2 в бу р

45 ферныи регистр 4. При этом на выходе элемента совпадения 9 формируется строб разрешения на управляющих входах вентилей ввода 6, Кроме того строб разрешения подается на элемент ИЛИ 8, деблокируя таким

50 образом установочные входы триггеров ин формационного регистра 3, и на выходной элемент переноса 5, разрешая формирование выхоцного сигнала, 4

2 — 2-вый импульс с фазовращателя 1ф проходит на выход и вводит в информационный регистр 3 число М„.л, равное прямому коду коэффициента деления.

B момент ввода прямой код коэффициен та деления преобразуется в обратный код поправки, т.е. в первый разряд информационного регистра 3 записывается единица, если первый разряд коэффициента деления содержит нуль, и остается равным нулю, еслипе вый разряд коэффициента деления содержит единицу. Нули в старших разрядах записываются в тех случаях, когда соответствующие старшие разряды коэффициента деления содержат единицьг, и наоборот.

Следукщий выходной импульс появляется через t>g, т.е, в момент перехода двух-э . тактного двоичного счетчика 2 из состояния 2 — 2 в состояние 2 -1, B этот же т Yl момент происходит очередной ввод поправки.

Формула изобретения

Делитель с переменным коэффициентом. деления, содержащий двухтактный двоичный счетчик, состоящий из информационного и буферного регистров и вентилей переноса на входе информационного регистра, вентили ввода и элемеит совпадения, о т л и ч а юшийся тем, что„. с целью расширения функциональных. возможностей в него введены элемент ИЛИ и инвертор, вход которого соединен с выходом. первого вентиля ввода, а выход — с установочным входом первого триггера информационного регистра, причем выходы остальных вентилей ввода подключены соответственно к установочным. входам остальных триггеров информационного регистра, входы элемента совпадения соединены с выходами триггеров буферного ре-. гистра, а его выход подключен ко входам. вентилей ввода, ко входу последнего вентиля переноса и к первому входу элемента ИЛИ, другой вход которого соединен с выходом первого триггера буферного регистра, а выход — со входом первого вентиля переноса.

Источники информации, принятые во внимание при экспертизе

1. Авт. св. СССР М 401005, кл.

Н 03 К 23/00, 1971 г.

2. Авт, св. СССР Лю 374750, кл.

Н С3 К 2 3/34, 1 971 г. (прототип) .

520689

Уулр

Составитель М. Аудринг 1 екред О. Луговая Корректор l1. Мельниченко

Редактор Б. Федотов

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 4969/220 Тираж 1 02 9 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам. изобретений и открьггий

113035, Москва, Ж-35, Раушская наб., д. 4/5