Дишифратор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii)520700

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву N 435587 (22) Заявлено 07.04.75. (21) 2121495/21 с присоединением заявки № (23) Приоритет— (51) M. Кле

Н 03 К 13/00

Государственный комитет

Совета Министров СССР оо делам изооретений и открытий (43) Опубликовано 05.07 76 Бюллетень № 25 (53) УДК 681.325.53 (088.8) (45) Дата опубликования описания 10.08.76 (72) Авторы изобретения

Д, М, Компанец, В. В, Федоровский, В. Д. Сагайдачный и В. П. Ковальчук (71) Заяви (54) ДЕШИФРАТОР

Изобретение относится к области телемеханики и предназначено для дешифрации сигналов телеуправления в каналах с комбинационным групповым избиранием для рассредоточенных объектов.

Известны дешифраторы по авт. св. N 435587.

С целью расширения функциональных возможностей дешифратора, в него введены настроечный узел, фиксатор группы, дополнительный элемент памяти, блокирующий и деблокирующий элементы, дополнительный элемент задержки и два элемента И. Входы настроечного узла соединены соответственно с выходами запоминающего узла и выходами узла взаимно сблокированных воспринимающих элементов, а выход — с первым входом фиксатора группы. Второй вход фиксатора и цепь его самоблокировки подключены к первому выходу элемента памяти, а третий вход — к инверсному выходу блокирующего элемента. Вход дополнительного элемента памяти через первый элемент И соединен соответственно с выходом буферного блокировочного элемента, с выходом элемента регулирования задержки, инверсным выходом деблокирующего элемента и с выходом второго элемента И, другой вход которого соединен со входом элемента регулирования задержки, а выход — с другим входом дополнительного элемента памяти, Второй выход дополнительного элемента памяти через дополнительный элемент задержки подключен к первому входу блокирующего элемента. Инверсный выход а фиксатора группы соединен со вторым входом блокирующего элемента, а другой выход — с первым входом деблокируюшего элемента. Второй вход деблокирующего элемента подключен к буферному запоминающему элементу, а третий вход и цепь самобло10 кировки — к буферному блокировочному элементу, при этом выход деблокирующего элемента соединен со схемой коммутации выходных цепей.

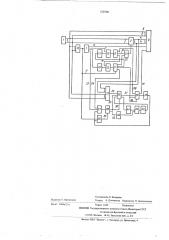

На чертеже показана блок-схема предложенного дешифратора, 15 Дешифратор содержит узел 1 взаимно сблокированных воспринимающих элементов, выходы 2 — 2я которых соединены со входами соответствующих фиксирующих элементов запоминающего узла 3.

Выходы 4, — 4н узла 3 совместно с выходами 5 — 5„ чп каждого воспринимающего элемента узла 1 включены в схему коммутации выходных цепей 6. В дешифратор входят также элемент регулирования задержки 7, буферный запоминающий элемент 8 с регулировкой длительности запоминания и буферный об блокировочный элемент 9.

52 700

Олин из выходов 2 — 2 " к ждого воспринимающего элемента узла 1 чере > эл лент ИЛИ 10 соединен со в одом элемента p(гулирования задержки 7 и с цепью самоблокировки i! буферного блокировочного элемента 9. Вход элемента 9 через элемент И 12 соединен с инверсным в.-ходом 13 элемента регулирования задержки 7 и с одним из прямых выходов

14 буферного запоминающего элемента 8. Вход элемента 8 через элемент И 15 соединен с одним из прямых выходов 16 элемента регулирования задержки

7 и инверсным выходом 17 буферного блокировочного элемента 9. Второй прямой выход 8 элемента регулирования задержки 7 соединен со схемой коммутации выходных цепей 6, а прямые выходы

19, 20 обоих буферных элементов 8, 9 через элемент ИЛИ 21 соединены общим входом запоминающего узла 3.

Выходы 2 — 2 узла 1 взаимно сблокированных воспринимающих элементов и выходы 4 — 4п запоминающего узла 3 соединены с настроечным узлом 22, Выход 23 элемента регулирования задержки 7, выход 24 буферного блокировочного элемента 9 и инверсный выход 25 деблокирующего элемента 26 через элемент И 27 соединены с дополнительным элементом памяти 28, имеющим цепь самоблокировки 29, которая через элемент И 30 подключена к инверсному выходу 25 деблокируюшего элемента 26 и к выходу элемента ИЛИ 10. Выход 31 дополнительного элемента памяти 28, выход 32 настроечно о узла 22 и инверсный выход 33 блокирующего элемента 34 соединены со входами фиксатора группы 35, имеющего цепь самоблокировки 36, которая соединена с выходом дополнительного элемента памяти 28. Выход 37 фиксатора группы 35, выход 38 буферного запоминающего элемента 8 и выход буферного блокировочного элемента 9 соединены со входами деблокирующего элемента 26, имеющего цепь самоблокировки 39, которая подключена к выходу буферного блокировочного элемента 9, выход 40 деблокирующего элемента 26 соединен со схемой коммутации выходных цепей 6.

Инверсный выход 41 фиксатора группы 35 и второй выход 42 дополнительного элемента памяти 28 через дополнительный элемент задержки 43 соединены со входами блокирующего элемента 34.

В канале с двухступенчатым комбинационным избиранием, где первой парой последовательных частотных импульсов избирается группа объектов, а второй парой из аналогичных частот избирается объект в группе, дешифратор работает следующим образом.

Первый частотный импульс сигнала, т.е. импульс первой (групповой) части его, воспринимается одним из взаимно сблокированных воспринимающих элементов узла 1 и через соответствующий выход и элемент ИЛИ 10 поступает на вход элемента регулирования задержки 7, с выхода которого через элемент И 15 проходит на вход буферного запомлнающего элемента 8, который становится на к1затко. временный режим запоминания, т.е. на период интервала между импульсами. Кроме того, первый l, ljQ

2О

ЭО

Ж

45 д я.

Ф ьЭ бО импульс через соответствующий выход узла 1 поступает на вход соответствующего фиксирующего элемента запоминающего узла 3 и кратковременно запоминается благодаря образовавшемуся сигналу на выхоле 19 буферного запоминающего элемента 8, который через элемент ИЛИ 21 поступает на вход запоминающего узла 3. Сигнал с соответствующего выхода 4 узла 3, который запомнил первый импульс, поступает на вход настроечного узла 22.

В интервале, .после исчезновения первого импульса, через инверсный выход 13 элемента регулирования задержки 7, прямой выход 14 буферного запоминающего элемента 8 и элемент И 12 срабатывает буферный блокироьочный элемент 9, Который своей цепью самоблокировки 11 подключается к выходу элемента ИЛИ 10, подает сигнал с выхода 20 через элемент ИЛИ 21 на вход запоминающего узла 3, отключает через инверсный выход

17 и элемент И 15 вход буферного запоминающего элемента 8, с выхода 24 подает сигнал на один вход элемента И 27.

Второй частотный импульс первой части сигнала, воспринятый одним из восприниь аюших элементов узла 1, через соответствующий выход 2 поступает на ьход настроечного узла 22, через выход 2 и элементИЛИ 10- в пель самоблокировки 11 буферного блокировочного элемента 9 и па вход элемента задержки 7. С выхода 23 последнего сигнал оступает на второй вход элемента И 27.

При этом, если на третий вход этого элемента постуnaåò сигнал с инверсного выхода 25 деблокируюшего элемента 26, то возбуждается дополнительный элемент памяти 28 на кратковременный режим запоминания, т,е. на пс риод интервала между импульсами. В период приема импульсов элемент памяти

28подпитываетсяпо цепи самоблокировки 29. Сигнал с выхода 31 элемента памяти 28 с выхода 32 настроечного узла 22 (в том случае, если настройка последнего совпадает с кодовой комбинацией, первой части сигнала, т.е. с кодовым признаком данной группы) и с инверсного выхода 33 блокирующего элемента 34 возбуждают фиксатор группы 35, который своей цепью самоблокировки 36 подключается к выходу дополнительного элемента памяти 28.

В начале приема второго частотного импульса буферный запоминающий элемент 8 обссточился, так как цепь его возбуждения была ооорвана инверсным выходом 17 буферного б.:окировочного элемента, а ресурс его кратковременного запоминания истек в начале приема второго импульса. Поэтому с возбуждением фиксатора группы 35 и появ1 пением сигнала íà его выходе 37 деблокируюший э)темент 26 не сработает и выходные цепи дешифратора будут заблокированы выходом 40 деблокирующего элемента 26.

В интервале после исчезновения второго импульса обесточиваются все элементы дешифратора, за исключением дополнительного элемента памяти

28, который через цепь самоблокировки 36 обеспечивает фиксацию воспринятого кодового приз520700 нака данной группы объектов, на который с помощью настроечного узла 22 был настроен дешифратор.

Третий чатотный импульс сигнала, т.е. первый импульс второй его части (исполнительной), воспринятый одним из воспринимающих элементов узла 1, аналогично первому импульсу первой части сигнала, поступает на соответствующиеэлементы схемы и фиксируется соответствующим фиксирующим элементом запоминающего узла 3, а затем с соответствующего выхода 4 узла 3 поступает на вход деблокирующего элемента 26, однако последний не срабатывает, так как буферный блокировочный элемент 9 пока обесточен.

В интервале (после исчезновения третьего импульса) элементы дешифратора работают, как и в интервале после исчезновения первого импульса сигнала. При этом сигнал с выхода срабатывающего буферного блокировочного элемента 9 поступает на вход деблокируюшего элемента 26. Последний срабатывает и своей цепью самоблокировки 39 подключается к выходу буферного блокировочного элемента 9; сигналом с выхода 40 элемент 26 деблокирует схему коммутации выходных цепей 6, а сигналом с инверсного выхода 25 отключает дополнительный элемент памяти 28, который, в свою очередь, выключает фиксатор группы

35, Четвертый частотный импульс сигнала, т,е. второй импульс исполнительной его части, воспринятый одним из воспринимающих элементов, через соответствующий выход 5, как и при приеме предыдущих импульсов, поступает в схему коммутации и выходных цепей 6и в комбинации с сигналом с соответствующего выхода 4 запоминающего узла 3 замыкает выходную цепь на соответствующий объект данной группы. Однако выходной сигнал включения объекта образуется только после срабатывания элемента регулирования задер>кки 7, который сигналом со своего выхода 18 окончательно разблокировывает схему коммутации выходных цепей 6. После исчезновения четвертого импульса все элементы схемы обесточатся и, таким образом, примут исходное состояние.

В случае когда настройка настроечного узла дешифратора не соответствует принимаемой кодовой комбинации первой части сигнала, срабатывает дополнительный элемент памятй 28, сиги» ом с выхода 42 через дополнительный элемент задер>, ки 43 возбуждает блокирующий элемент 34, который сигналом с инверсного выхода 33 блокирует вход фиксатора группы 35. В таком состоянии дешифратор остается до конца приема всего сигнала, после чего возвращается в исходное состояние.

Формула изобретения дешифратор по авт. св. N 435587, о т л ич а ю шийся тем, что, с целью расширения его

Я Ь функциональных возможностей. введены настроечный узел, фиксатор группы, дополнительный элемент памяти, блокирующий и деблокируюншй элементы, дополнительный элемент задержки и два элемента И, причем вхоцы настроечного узда соединены соответственно с выходами запоминаю«эО щего узла и выходами узла взаимно сблокированных воспринимающих элементов, а выход — с первым входом фиксатора группы, второй вход которого и цепь его самоблокировки подключены к нер

Я вому выходу элемента памяти, а третий вход к инверсному выходу блокирующего элемента, при этом вход дополнительного элемента памяти через первый элемент И соединен соответственно с выходом буферного блокировочного элемента, с выходом элемента регулирования задержки, инверсным выходом деблокируюшего элемента и с входом второго элемента И, другой вход которого соединен со входом элемента регулирования задержки., а выход — с другим входом дополнительного элемента памяти, второй выход которсго через дополнительный элемент задержки подключен к первому входу блокирующего элемента, кроме того инверсный выход фиксатора группы соединен с вторым входом блокирующего элсменО та, а другой выход — с первым входом дебдокируюшего элемента, второй вход которого подключен к буферному запоминающему элсме I Tv, а третий вход и цепь самоблокировки — к буферному блокировочному элементу, при этом выход деблокирующего элемента соединен со схемой коммутации выходных цепей.

520700

Редактор Т. Орловская

Заказ 3084а/255

Составитель Л. Захарова

Техред A. Демьянова Корректор Н. Золотовская

Тираж 1029 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4