Анализатор информации для устройств телеконтроля циклического действия

Иллюстрации

Показать всеРеферат

ОПИСА

ИЗОБРЕТ

К АВТОРСКОМУ СЬИ

Союз Советских

Социалистических

Республик (61) Дополнительное н авт.

«( (22) Заявлено18.02. 74 (21) . Мл.

08 С 25/00

94 l 1(00 с присоединением заявки Х (23) Приоритет(43) Опубликоваио1 5.07. 7 (45) Дата опубликования

14еуйьрстеениый иоиитет

Сооата Иимистрое СССР оо делан изобретений и открытий

ДК 621.398 (088.8р (72) Авторы изобретении

А, Г. Мелик-Аскаров, В. П. Биндюк и В. Г. Черттьтх (71) Заявитель

Институт автоматики (54) АНАЛИЗАТОР ИНФОРМАЦИИ ДЛЯ УСТРОЙСТВ

ТЕЛЕКОНТРОЛЯ ЦИКЛИЧЕСКОГО ДЕЙСТВИЯ

i пии, 1

Устройство относится к области промыть ленной электроники.

Известны анализаторы ннформапии для устройств телеконтроля пикнического дейст вня, содержлиие дешифратор кода парамет-. ра, первая груши выходов которого подклю,чена к первой группе входов блока сравне ния, присоединенного второй группой входов через группу элементов ИЛИ-НЕ к адрес- ,ным шинам, а двуми выходами - к первому 10 и второму входам блока ключей, выходы которого соединены с соответствуютпими входа ми блока памяти отклонений.

Однако известные устройства обладают недостаточно высоким быстродействием. 1а

Предлагаемое устройство отличается от известных тем, что оно содержит дополни тельный блок сравнения, первая и вторая группы входов которого подключены соответственно к второй группе выходов дешифрато-20 ра и через дополнительную группу элементов ИЛИ-НЕ - х адресным шинам, допол:нительньтй блок ключей, первый и второйвхо-:

".ды которого подключены к соответствукипим выходам дополнительного блока сравнения, 2б

2 а третий вход соединен с третьим входами ! основного блока ключей и с шиной оазреше; ния, и дополнительный блок памеети отклаетений, ъ, входы которого подключены к соответствующим выходам дополнительного блока ключей, что значительно повышает бьтстродействив анализатора и расширяет область его примана ния.

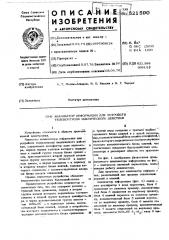

На фиг. 1 изображена рлок-схема пред ввгавмого вивливатора имрормаиии; иа фиг,, .

2 — диаграмма значений параметров, пояс ивюювв работу аивливатора.

Для простоты дан анализатор информаразличакилий два предела отклонения:.верхний и нижний.

Анализатор информадии (фиг. 1) оодер-! жит дешифратор 1 кода параметра, блок 2

i сравнения по нижнему пределу, дополнитель ный блок 3 сравнения по верхнему пределу, блок 4 ключей переноса по нижнему праде, лу, дополнительный блок 5 ключей перено- ! са по верхнему пределу, блок 6 памяти o, клонений по нижнему пределу, дополнительный

1 блок 7 памяти отклонений по верхнему претделу, элементы ИЛИ-НЕ 8 -8; вход 9 щи.521590 пульса разрешения, соответственно нижней и верхней, выходы 10 и 11 на индикацию отклонений от пределов нормы и адресные шины 12 12 .

В анализаторе информации дешифратор 1

:двоичного кода параметра своими входами под1 кпючен к трем старшим разрядам пятираэрядного@воичного счетчика-регистра приема и преобразования информации тепеизмерения (на . фяг. 1 яе показан), s котором поспедоватепь Р но во времени фиксируется (в режиме .цккпнчзской работы системы тепемеханики) ве}личина измеряемого параметра каждого ад- реса (обьекта) тепеизмерения, При таком подключении дешифратор 1 двоичного кода параметра обеспечивает шаг квантования,j

:равный Четырем единицам кода, а число с

nese@ квантования на его выходе равно во ми; 0 4-8-12-16-20 24-.28 (разряди двоичного счетчика, фиксирующего код пар метра, а также шаг квантования при кон тропе выхода параметра за пределы нормы

1 могут быть любыми и выбраны дпя поясне;ния попагаемого произвольно) .

Восемь ступеней контроля, которыми

;представпен параметр на выходе дешифрато " pa 1 двоичного кода параметра, раздепены

:,на две группы: нижнюю и верхнюю. Нижняя

,группа включает в себя четыре нижних сту : i l0 пени дешифратора j. двоичнот"о кода параме ра от 0 до 12, верхняя-четыре верхних

:ступени от 16 до 28, Первые четыре выхо I

Iàà дешифратора 1 двоичного кода параметра,, относящиеся к нижней группе, подключены

;5 соответственно к цервому, второму, третье-,, му и четвертому входу блока 2 сравнения е

I заданными установками зоны разрешенных значений по нижнему пределу, а вторые чеI тыре выхода дешифратора 1, относящиеся к:, „ ерхней группе, подключены соответственно l первому, второму, третьему и четвертому, %5Rollg бпока 3 сравнения по верхнему пре депу, Остальные четыре входа: четвертый, пять@, шестой, седьмой и восьмой блока 2 .@

I сравнения по нижнему пределу и блока 3 сравнения по верхнему пределу подключены через о элементы " ИЛИ-HE 8 -8 к соответствую»

1, аким уставкам зоны разрешенных значений, соединенным с адресными шинами 12 -12 .,Ь

Х

Блоки 2и Зсравнения по нижнему и верх} ему пределам идентичны между собой. Каж дый из инх состоит из четырех двухвходовьбс схем И, одной сборки ИЛИ и триггера Шмид- та {на фиг. 1 не показаны). Первые входы: Ю схем И являются непосредственно первым, вторым, третьим и четвертым, а вторыепятымр шестым седьмым и восьмым BxogG

1 ми бпоков 2 и 3 соавнения. Выходы схем

И каждого иэ блоков 2 и 3 сравнения через 60

4 диодную сборку ИЛИ подключены K тригге;ру Шмидта, выходы последнего являются не .посредственно первым единичным" и вторым нупевым" выходом каждого бпока сравне + ния, Первый и второй выходы блока 2 сравнр,, ния по нижнему пределу соединены с перв !

Im вторым входами блока 4 ключей перенос по нижнему пределу, а первый и второй .вы= : ходы блока 3 сравнения по верхнему пре

;делу соединены с первым и вторым входа ми бпока 5 ключей переноса по верхнему

,пределу, Кроме того, третьи входы блоков !

4 и 5 ключей переноса по нижнему и верхр ,нему пределам подключены к входу 9 ,пульс разрешения, а остальные входы зт ,блоков соединены с соответст;вующими ад ресными шинами 12 -12.

Н

Блоки 4 и 5 переноса по верхнему и нему пределам состоят из И пар схем И

;совпадения, причем каждая пара схем И пе выми входами соединена с соответствующе

;адресной шйной, Вторыми входами первые схемы И каждой пары связаны с первыми

:,"единичными", е вторые о вторыми вуич »

„выми входами этих блоков. Кроме того, ( все схемы И совпадения бпоков 4 и 5 печ

,реноса связаны с третьими входами соотве} ствующих блоков и имеют индивидуальные .выходы - единичный и нулевой" дпя кажр ° .дой пары.

Выходы блока 4 переноса информации п<

I нижнему предепу соединены с соответствую,,щими входами блока 6 памяти отклонений

I, от нормы по нижнему пределу, а выходьгбпо ка 5 переноса информации по верхнему пре делу - с соответствующими входами блока .7 памяти отклонений по верхнему пределу.

Блоки 6 и 7 памяти отклонений от нор- мы по нижнему и верхнему пределам состо. ! ят из П отдельных ячеек памяти (тригге ., ров), выходы 10 и 11 которых соединены с соответствующими индикаторами (на фиг,,1 не показаны), расположенньпми на пульте оператора или мнемошите.

В исходном состоянии ко всем адресньпч шинам 12 -12 . приложены потенциалы за

ri прета, при этом от соответствующих элементов ИЛИ-HE 8 -8 (включая те иэ них

1 и, и которые не имеют с6изи с уставками) к пятому, шестому, седьмому и восьмому входу блоков 2 и 3 сравнения по верхнему и ниы. нему, пределам приложены потенциалы разрешения. В результате, в зависимости от значения величины параметра телеизмерения, т. е. в зависимости от того, какой из выходов дешифратора 1 в данном случае окажет » .ся возбужде, возбуждается первый еди":>:ичный" выход блока 2 сравнения по нижнь521 500

5 ! му пределу или блока 3 сравнения по верх- нему пределу, который, в свою очередь, под,ключает потенциал разрешения z первому

I" °

"единичному входу блока 4 или блока 5 п

>реноса по верхнему или нижнему пределу. !

>Однако ко всем остальным входам блоков ,4 и 5 переноса в данном случае прикладь ! ваютса потенциалы запрета, и все триггер ,блоков 6 и 7 памяти отклонений по верхи ,му и нижнему пределам остаются в том п 1О ложении (О или 1"), в которое они были йерекиочены на предыдущем цикле опро» са, В режиме циклической работы системы телемеханики, адресов телеизмерениа при . >5 опросе поочередно воэбуждаютса от адрес ного дешифратора системы шины 12 -12, 1 я на каждом очередном адресе в момент ср

1пения кода параметра с заданной уставкой

J на вход 9 анализатора поступает импульс

> разрешения or блока синхронизации системы.

Возбужденная адресная шина, например ,шина 12, подготавливает разрешение на со ответствуюцшх входах блоков 4 и 5 ключе перечоса по нижнему и верхнему пределам

:и посредством уставки зоны разреЬнних значений возбуждает элементы ИЛИ-HE 8, 3 >

>.8 и 8, при этом элементы ИЛИ-HE 8 и 8 подключают потенциалы запрета на

4 седьмой и восьмой вход блока 2 сравнения

1 по нижнему пределу, а элемент ИЛР1-HE 8 на пятый вход блока 3 сравнения по верх нему пределу. Входы в блоки 2 и 3 сравне

35 ния по верхнему и нижнему пределам от Эле :,ментов ИЛИ-HE 81-8 управляют (накла 4 дывают запрет или разрешение) соответст

;вующими входами и эти блоки от дешифра— тора 1. Так, например„пятый вход управ -! 4О

>ляет входом первым„. шестой вход - aropIQ !

>входом, седьмой — третьим, а восьмой,:четвертым входом.

Если параметр телеизмерения, соответ,ствующий адресу шины 12„, находится в 45 ,пределах нормы, заданных уставкой зоны

>разрешенных значений, т, е. возбужден один из выходов 8 "> "12 или 16" дешифратора 1 двоичного кода параметра, к которым ,подключены >потенциалы запрета от соответ

5О, ствующих элементов ИЛИ -КЕ 8, 8 и

»

>8 то возбуждаются вторые "нулевые вы5> ходы блоков = и 3 сравнения IIo верхнему . и нижнему пределам,, которые„в свою оче- 55

:редь, подготавливают потенциалы разрешеHHH FfG втор ых E i(0JxQFE бл0к Ов 4 и ..> KIIIo I0É, переноса по нижне.,>у и верхнему пределам, и результате чего >>ри г>опкч>очен»и импульса раэреше>н>я:0 в> ;»>у >; в,>>I>J:..г>>ра, 60 соединенному с третьими входами блоков !

4 и 5 ключей переноса, возбуждается одна

>из схем совпадения И этих блоков, блтго -

l дара чему триггерьЪ блоков 6 и 7 памяти

:отклонения параметра по верхнему и нижне му пределам, соответствующие адресу шины

>12, переключаются в положение "О», >

Если параметр, соответствующий адресу .шины 12 „выходит за нижний предел эоны разрешен ых значений, т. е. возбужден один из выходов "О или "4» дешифратора 1 двф >ичного кода параметра, к которым подклю, чены потенциалы разрешения от соответст -:

1 ,вующих элементов ИЛИ-HE 8 и 8, то ,возбуждается первый единичный выход ! блока 2 сравнения по нижнему пределу, прй

>этом в блоке 3 сравнения по верхнему аре,делу возбуждается второй нулевой выход.

> .Возбужденный первый выход блока 2 подго тавливает потенциал разрешения на первом единичном" входе блока 4 ключей переноj,са по нижнему пределу, а возбужденный вт6jpoA выход блока 3 - потенциал разрешения

-на втором нулевом входе блока 5 ключей переноса по.верхнему пределу, следователь но, при подключении импульса разрешения, .по входу 9 анализатора информации возбужjI ! даются по третьему входу соответствующие, > ,.схемы совпадения блоков 4 и 5, посредст,jism которых триггер блока 6 памяти откло»"«ений по нижнему пределу адреса шины 12 переключаются в положение 1, а триггер, (.

;блока 7 памяти отклонений по верхнему пре делу адреса шины 12 - в положение "О".

Если параметр, соответствующий адресу

>, шины 12, выходит за верхний предел зо>> ,ны разрешенных значений, т. е. возбужден Ьдин из выходов "20", "24 или "28" деЙифратора 1 двоичного кода параметра, к которым подключены потенциалы разрешения от соответствуюших элементов ИЛИ-HE 8

8 или 8, то возбуждается небитый еди —; ничный выход блока 3 сравнения по верхнему пределу„при этом в блоке 2 сравнения по нижнему пределу возбуждается второй "ну,левой выход. Возбужденный первый выход

,олока 3 подготавливает потенциал разреше ния на первом "единичном" входе блока 5 ,переноса по верхнему пределу, а возбужденный второй выход блока 2 — потенщял раз решения HB втором "нулевом" выход» блока

4 ключей переноса по нижнему IIpeIIeIIy.

Таким образом, при подключении кмпугн са разрешения к входу анализатг>р>1» формации возбуждаются по tpBTE 0. .",>у pxi>i> > t >nr

ВЕтСтВУЮШИЕ СХЕМЫ 00ВПаЛ>»ц» .>;I»F г i !<

5, посредством которых fp! гг! и >".а-»; >>:> мяти oTKII0F>oний но нег>х»>".>у»i::Ii »

52) г ОО

Физ. 1

i KM са шины 121 переключается в положение

"1, 9 триггер блока 6 памяти отклонений по нижнему пределу адреса шины 12 — в

1 положение О .

Аналогичным образом в течение. никла опроса производится сравнение с заданными

l уставками эоны разрешенных значений всех остальных адресов контролируемых парамет-, ров, триггеры блоков 6 и 7 памяти откло пений по верхнему и нижнему пределам за- я ннмают соответсчъукхцие положения.

Ф ормула изобретения

l5

Анализатор информации для устройств телеконтроля пикнического действия, содер- жащий дешифратор кода параметра, первая группа, выходов к .хт1фого подклк"чена K не 3 вой группе входOB блока; оавн ния поисое„, I диненного второй группой входQB чер-еэ груп-) и пу элементов ИЛИ-П1: к адресным шЬжм, а двумя выходами - к первому и второму входам блока ключей, выходы которого сое- динены с соответствуюшими входами блока памяти отклонений, о т л и ч а к> ш и йс я тем, что, с пелью иовьянения быстродействия и расширения области применения, он содержит дополнительный блок сравнения, первая и вторая группы входов которо- го подключены соответственно к второй группе выходов дешнфратора и через дополни -, тельную группу элементов ИЛИ-НЕ - к адрес- ным шинам, дополнительный блок ключей, первый и второй входы которого подключены к соответствуюшим выходам дополнительно го блока сравнения, а третий вход соединен с третьим входом основного блока ключей ., 1 и с шиной разрешения, и дополнительный блок памяти отклонений, входы которого подключены к соотьетствуюшим выходам дб полнительн ого бл ока ключей.

ИПИИПИ Заказ 4674/53З

Тираж 829 Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4