Ясейка памяти

Иллюстрации

Показать всеРеферат

ОП И(:АЙЙЕ

К ЗОЬРЕТЕ И ИЯ К АВ7ОРСИОМУ СВИДПЕДЬСТВУ г

Союз Советских

Социалистических

Республик (11) 521605 (61) Дополнительное к авт, свид-ву(22) ЗаявленоОэ,p1,74 (21) 1982487/24 (51) М. Кл. (з11 С 11/40 с присоединением заявки №

Государственный комитет

Совете Министров СССР па делам иеаоретений и открытий (23) Приоритет (53) УДК 581.327,6 (088,8) (43) Опубликовано 15.07.76.Бюллетень № 26 (45) Дата опубликования описания!15.12.76

Л. П. Домнин, Л. Н, Петров, А. H. Маковий, А. С. Савлук и Д. П. Федоров (72) Авторы изобретения (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к вычислительно технике и может.бйть использовано при по -! строении быстродействуюших запоминаюших . ,устройств с малой потребляемой мощностьк .

Известна ячейка памяти, содержашая ,многоемиттерные и загрузочные транзиотооы ! с триггерными связями (11. Эта ячейка ,памяти имеет низкую помехоустойчивость (и термостабильность. Наиболее близкой к изобретению является ячейка памяти, содер,» 0 жашая диоды, усилительные многоэмиттер-, ные транзисторы и нагрузочные транзисто--! .Ipsr, коллектор первого из которых соединетп с первым .эмиттером первого и базой втор го усилительных транзисторов, коллектор .второго нагрузочного транзистора соединен с первым эмиттером второго и базой перво;го усилительных трачзисторов (21. Однако и эта ячейка имеет низкую помехоустойчи» вость и термостабиж,ность и невысокое быстродействие.

Цель изобретения — повышение быстродействия„помехоустойчивости и термостабильности, В предлагаемой ячейке это дости гается тем, что в нее включены первый и вто-, yoN дополнительные транзисторы, причем база первого нагрузочного транзистора сои

;единена с катодом первого диода и коллекто ром второго дополнительного транзистора, база второго нагрузочного транзистора со:единена с катодом второго диода и коллек

"тором первого дополнительного транзистора, эмиттеры дополнительных транзисторов дод- ключены к коллекторам усилительных тран-: зисторов, а базы дополнительных транзисто -! ров подключены к базам соответствующих

l усили тельных транзисторов.

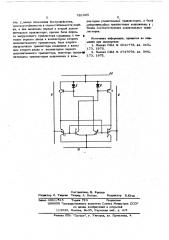

На чертеже представлена дринпипиальная

:,:схема предложенной ячейки.

Ячейка памяти содержит два инверсно включенных усилительных . многоэмиттерных транзистора 1 и 2, коллекторы которых соединены между собой и образуют обшую ,коллекторную связь, что значительно умень» шает размер ячейки при ее интегральном исполнении. Первые эмиттеры транзисторов

1 и 2 соединены с коллекгорами нагрузо :иых ! транзисторов противоположного гипа проводимости Э и 4, выполнаюших роль активных динамических нагрузок, у которых эмит теры соединены между собой и подключены к анодам диодов 5 и 6 и источнику питания.

Базы транзисторов 3 и 4 соединены соответственно с коллекторами дополнительных транзисторов 7 и 8, базы которых подключены соответственно к базам многоэмиттер1 . ных усилительных транзисторов 1 и 2 и к коллекторным цепям нагрузочных транзисто:

1 ров 3 и 4 противоположных плеч. Эмиттерш дополнительных транзисторов .7 и 8 соедин - 1О ны между собой и подключены к коллекто рам транзисторов 1 и 2. Вторые эмиттеры транзисторов 1 и 2 подключены к разрядным шинам 9. Коллекторы транзисторов 1 и 2 подключены к адресной шине 1О. Вся ячей-. 1к ка строго симметрична.

В одном из состояний ячейки потенциал баэ многоэмиттерного транзистора 2 и транзистора 8 выше, чем потенциал. баз трап-1 зисторов 1 и 7 относительно коллекторов щ транзисторов 1 и 2. В этом случае образу, ются два кольца с замкнутой положитепьной ,:обратной связью. Первое кольцо состоит из соединенных между собой коллектора трвн- .

1 эистора 3, баз. транзисторов 2 и 8, коллек-. Я тора транзистора, 8 и базы транзистора 3 с катодом диода 5, являющегося одновре-,. менно нвгрузочным элементом транзистора 1 ,8, а также параметрическим термостабили- i

1 т . затором базового тока транзистора 3. Вто, ЗО рое кольцо, симметричное первому, состо-,; ит из соединенных между. собой коллектора транзистора 4 с базами транзисторов

1 и 7,:коллектора транзистора 7 и базы транзистора 4 с катодом диода 6-.

При повышении потенциала беэ транзистд-! ров 2 и 8 потенциал. коллектора транзис тора 8 и первого эмиттерв транзистора 2 понижвются, что приводит к увеличению тока 4О через прямосмещеиный диод 5„a это в своЬ. ,очередь приводит к увеличению тока базы транзистора 3 и к повышению коллекториого тока этого транзистора, Повышение тока коллектора транзистора 3 ведет к увеличе»,щ нию базовых токов трвнисторов 2 и 8, т. е. к еще большему повышению потенциала баз .транзисторов 2 и 8. Весь процесс происходит.:в активном режиме до значения коэф фициентв усиления по кольцу обратной свя,чО эи, равного единице. При этом потенциал кол- лектора транзистора 8 приближается к по

-тенцивпу его эмиттерв, в потенциал коллекгора транзистора 3 приближается к: потенци- алу его эмиттерв. Поскольку потенциал пер,йб ваго эмиттерв транзистора 2 стремится к потенциалу его коллектора, то в этом слу чае потенциал баз транзисторов 1 и 7 по нижвется, что ведет к звлирвнию этих трвн зисторов. При этом уменьшенный ток через {ф

4 диод 6 снижает ток базы транзистора 4 и, следовательно, ток его первого коллектора, V. е. ток первого эмиттерв транзистора;.. 2. Благодаря наличию кольца положительной обратной связи процесс происходит в актив» ном режиме до значения коэффициента уси- ленйя, равного единице. Токи транзисторов

1, 4 и 7 резко уменьшаются и транзисторы находЯтсЯ на гРанице Режима отсечки. Пос ольку ток первого эмиттера транэистора2; езко снижен,. а ток базы приближается к величине,тука коллектора транзистора 3, то- транзистор 2 по первому эмиттеру sxo дит в режим насыщения. Так как коэффици енты усиления транзисторов 7 и 8 относи- : тельно высоки, то за счет термостабиль- 1 ной положительной обратной связи устойчи вое состояние ячейки сохраняется;,при рабс те в широком интервале температуры и пи- тающих напряженяй, а также при весьма з ачительных токах разрядных шин, т. е. бистабильностьсостояния и помехоустойчивость ячейки повышаются.

Потребление тока происходит по цепи, 1 транзистор 3-базы" транзисторов 2 и 8-коллектор транзйстора 8. другое плечо ячейки находится в состоянии, близком к состоя ттию отсечки и ток не потребляется. азиопы Б и 6 являются не только эле:ментами нагрузки в кольце обратной связи, но и выполняют функции термоствбильности базовых токов транзисторов 3 и 4, что улучшает термостабильность ячейки при работе в широком диапазоне. температуры. Поскольку транзисторы 3 и 4 являются активными динамическими нагрузками транзисторов 1 и 2, т. е. сами выполняют функции усиления сигнала и, следовательно, транзисторы 2 и 1, 8 и 7 и их базы являются нвгрузочными элементами транзисторов 3 и 4, то про . цесс нарастания величины импульса проис-. ходит с высокой скоростью.

Испытания предложенной ячейки памяти

1 показали, что она имеет высокое быстродействие и помехоустойчивость при высокой термоствбильности.

Формула изобретени я

Ячейка пвмяти, содержащая диоды, усвлительные многоэмиттерные транзисторы и нагрузочные транзисторы, коллектор первого из которых соединен с первым эмиттером первого и базой второго усилительных травэисторов, коллектор второго нвгрузочиого транзистора соединен с первым эмиттером второго v, базой первого усилительных трввэисторов, о т л и ч в ю а в я с я тем, 521605 что, с. целью повышении быстродействия,, помехоустойчивости и термостабнльности ячей-.

«и, в нее включены первый и второй полол нительные транзисторы, причем база первого нагрузочного транзистора соединена.с катодом первого диода и коллектором второго дополнительного транзистора, база второго нагруэочного транзистора соединена с като дом второго диода и ..коллектором первого дополнительного транзистора, амиттеры допсд-Зф иительных транзисторов подключены к кол

6 ,:лекторам усилительных транзисторов, а баэь дойолннчелйпыiх транзисторов подключены K j ! базам соответствуюаих усилительных тра ; эис торов.

Источники икформании, прилитые во вн(ь» . мание при экспертизе:

1. Патент США % 3531778, кл. 340

:173, 1970.

2. Патент США М 3747076, кл. 340 ; 173, 1972.

Составитель В. Фролов

Редактор Л. Тюрина Техред А. Богдан Корректор: Б.Югас

Заказ 4861/515 Ткраж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР ло делам изобретений и открытий

113035, Москва, Ж35, Раушскаи иаб., д, 4/5 . Филиал HAli Патент, г. Ужгород, ул. Проектная, 4