Устройство для контроля кодовых жгутов постоянных запоминающих блоков

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 10.12.7 (21) 2082458/24 (11) 52 1609.

2 (51) М. Кл.

G 11 С 29/00 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.07 76 бюллетень _#_ 26 (53) УДК 681.Э27

Гасударственный комитет

Совета Министров СССР оо делам изобретений н открытий (088.8) (45) Дата опубликования описания 16.12.76 (72) Авторы изобретения

A. В. Карлов, А. Д. Белов и E. В. Кушелев (71) Заявитель (54) УСТРОИСТВО ДЛЯ КОНТРОЛЯ КОДОВЫХ ЖГУТОВ

ПОСТОЯННЫХ ЗАПОМИНАЮШИХ БЛОКОВ

Изобретение относится к области запоминающих устройств, в частности, кустройствам для контроля кодовых жгутов постоянных запоминающих блоков.

Известны устройства для контроля постоянных запоминающих блоков, содержащее регистр, счетные входы которого соединены с вентилями, сигнальные их входы,подключены через разрядный коммутатор к выходу постоянного запоминающего блока, уп- 10 равляющие входы подсоединены к выходам триггеров счетчика адресов, а раздельные входы регистра соединены с блоком установки fl).

Известные устройства обеспечивают вы- !5 сокую надежность контроля блоков постоянной памяти. Однако они имеют ограниченную точность контроля кодовых жгутов постоянных запоминающих блоков, так как не учитывается специфика съема информации с кодовых жгутов и не обеспечивают достаточной достоверности считывания с них информации.

Наиболее близким техническим решением к настоящему изобретению является устройство для контроля кодовых жгутов постоянных запоминающих блоков, содержащее регистр числа, выходы которого подключены к одним входам блока сравнения, а его вторые входы соединены с выходами постоянного запоминающего блока, а выход - с блоком управления, подключенным к счетчику адресов соединенному со Входом постоянного запоминающего блока, блок вентилей, информационные входы которого подключены ко вторым входам блока сравнения, управляющие входы объединены и подключены к блоку управления, а выходы подключены ко входам регист. ра числа (2), Известное устройство имеет достаточные быстродействие и надежность контроля постоянных запоминающих блоков, однако оно имеет ограниченную достоверность проверки, информационных параметров кодовых жгутов постоянных запоминающих блоков в связи со сложностью и возможной неточностью укладки кодовых жгутов в поле чувствительных элементов.

Помимо этого, известное устройство обладает недостачной достоверностью считываемой информации с кодового жгута, так как

521609 считываемая информация зависит от целестности сердечников, плотности прижатия ярма к сердечнику зависимости достоверности информации от параметров магнитопровода.

Кодовый жгут при проверке на известном устройстве может быть поврежден (обрыв, нарушение изоляции, замыкание кодовых шин между собой и т.п.) в результате укладки его в поле сердечников, замыкания магнитопровода и при извлечении жгута из последнего.

С целью повышения надежности работы устройства, точности и достоверности результатов контроля оно содержит блок интегрирования и блок компенсации помех, входы которого подключены к соответствующим выходам программного блока и адресного коммутатора, а выходы — к входам блока воспроизведения и адресного коммутатора и первым входам блока интегрирования и дискриминатора, выход блока воспроизведения через последовательно соединенные коммутатор разрядов и блок дифференциальных усилителей подключен к второму входу блока интегрирования, второй вход диокриминатора подключен к выходу блока интегрирования, а выход — к второму входу блока сравнения.

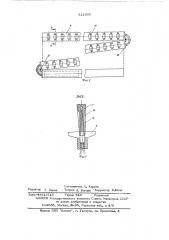

На фиг, 1 изображена схема предлагаемого устройства; на фиг, 2 — общий вид блс ка воспроизведения; на фиг, 3 — индуктивный датчик.

Устройство для контроля кодовых жгутов постоянных запоминающих блоков работает

)ф следуюшим образом.

Прогаммный блок 1 выдает на адресный коммутатор 2 код адреса числовой шины кодового жгута 10, по которому адресный коммутатор 2 посылает импульс тока опро® ca. В зависимости от того, с какой стороны от датчика ll проходит выбранная числовая шина кодового жгута 10, на обмотках 12 наводятся разнополярные сигналы, определяющие заложенную в жгутинформацию, ® соответствуюшую состоянию" l" или "0". На один из инцук тивных датчиков 1 1 (среднюю точку обмоток 12) подается с адресного коммутатора 2 импульс стробирования, выводящий через коммутатор 5 разрядов усилители тока блока 6 в область работы, чувствительную к сигналам выбранной группы индуктивных датчиков 11. Сигналы с других (невыбранных) индуктивных датчиков ll у не поступают на усилители блока 6 за счет запирающего действия сигналов коммутатора 5 разрядов.

Информационные сигналы, предварительно усиленные блоком 6, поступают в блок 7

40 интегрирования, в котором они преобразуются в однополярный сигнал, а затем поступают на вход дискриминатора 8, с выхода последнего информационные сигналы поступают в блок 3 сравнения, определяюшийсоот46 ветствие этих сигналов сигналам, заданным программным блоком 1, При однозначном соответствии информации, считанной с кодового жгута 10, и эталонной информации, блк 3 сравнения выдает соответствующую

®команду на переход к проверке следующего информационного участка кодового жгута 10.

С целью выравнивания токов опроса, для обеспечения равнозначной передачи разрядных сигналов с кодового жгута 10 на блок 4 воспроизведения и для исключения зависимости параметров сигналов от положения выбранной разрядной шины кодового жгута 10 в цепь опроса разрядных шин включен выход блока 9 компенсации помех, выравнивающего сигналы опроса между кодовыми шинами

Устройство для контроля кодовых жгутов постоянных запоминающих блоков содержит программныйблок 1, под слюченный к адресному коммутатору 2 и первому входу и выходу блока 3 сравнения, блок 4 воспроизведения, коммутатор 5 разрядов, блок 6 дифференциальных усилителей, блок 7 интегрирования, дискриминатор 8, блок 9 компенсации помех, соединенный с проверяемым кодовым жгутом 10.

Входы блока 9 компенсации помех подключены к соответствующим выходам программного блока 1 и адресного коммутатора 2, а выходы — к входам блока 4 воспроизведения, адресного коммутатора 2, первым входам блока 7 интегрирования и дискриминатора 8, Выход блока 4 воспроизведения через последовательно соединенные коммутатор

5 разрядов и блок 6 дифференциальных усилителей подключен к второму входу блока

7 интегрирования, второй вход дискриминатора 8 подключен к выходу блока 7 интегрирования, а выход - к второму входу блс ка 3 сравнения

Блок 4 воспроизведения выполнен (фиг 2 и 3 ) в виде набора индук тивных датчиков 1 1, на которых размещены проверяемый кодовый жгут 10. Каждый из датчиков 11 содержит по две бифилярные обмотки 12, Начало первой и конец второй обмоток 12 объединены, закрыты защитными колпачками 13, имеющими вертикальные прорези 14 для обвяэки кодовых жгутов 10, а группы диэлектрических индуктивных датчиков 4 соединены посредством шарниров 15 в последовательную цепь.

521609

Источники информации, принятые во внимание при проведении экспертизы;

l. Авторское свидетельство СССР № 273281, опубликованное по кл. G 11 С

29/00 05.11,1969г, Формула изобретения р 2. Авторское свидетельство СССР

Устройство для контроля кодовых жгутов № 364967 опубликованное по кл. G 11 С постоянныхзапоминаюших блоков, содержащее 29/00 28.12,1972г, жгута 10 в зависимости от их взаимного расположения и от величины тока, протекающего по опросной цепи. Блок 9 компенсации помех 9 также отделяет рабочие сигналы от помех по амплитудно-временным параметрам,i

Соединением блока 9 с блоком 7 интегрирования достигается выравнивание всех информационных сигналов и приведение их к средней величине.

Таким образом, при использовании пред- Io лагаемого устройства повышается качество кодовых жгутов за счет исключения возможности их повреждения при контроле; создается возможность исправления информации в кодовых жгутах с исключением из них ко-15 довых проводов с ложной информацией,что улучшает характеристики кодовых жгутов, так как отсутствие лишних проводов уменьшает емкость монтажа и улучшает динамические параметры постоянных запоминающих блоков; повышается достоверность считываемой информации за счет компенсации помех; обеспечивается использование универсального приспособления для изготовления и контроля кодовых жгутов; повышаеч ся качество и производительность труда, программный блок, подключенный к адресному коммутатору и к первому входу и выходу блока сравнения, блок воспроизведения, коммутатор разрядов, блок дифференциальных усилителей и дискриминатор, о т л и ч а— ю щ е е с я тем, что, с целью повышения надежности работы устройства и точности контроля, оно содержит блок интегрирования и блок компенсации помех, входы которого подключены к соответствующим выходам программного блока и адресного коммутатора, а выходы — к входам блока воспроизведения и адресного коммутатора и первым входам блока интегрирования и дискриминатора, выход блока воспроизведения через последовательно соединенные коммутатор разрядов и блок дифференциальных усилителей подключен к второму входу блока интегрирования, второй вход дискриминатора подключен к выходу блока интегрирования, а выход - к второму входу блока сравнения.

521609 Риг 2 дидА

Составитель А. Карлов

Редактор Г Янова Техред A. Богдан Корректор Б,Югас

Заказ 4861/515 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4