Фзовый дискриминатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») 521649 (61) Дополнительное к авт. свид-ву (22) Заявлено 28 03.75 (21) 2117685/21 с присоединением заявки №вЂ” (23) Приоритет—

2 (51) М. Кл.

Н 03 > 13/00

Н 03 К 5/18

Гасударственный комитет

Совета Министров СССР па делам изобретений и OTKpbtTHN (43) Опубликовано15.07.76,Бюллетень №26 (53) УДК 621.374.3 (088.8) (45) Дата опубликования описания 07.10.76 (72) Авторы изобретения

В. А. Барков и В. А. Шабаев (71) Заявитель (54) ФАЗОВЫЙ ДИСКРИМИНАТОР

Настоящее изобретение относится к импульсной технике и может быть использовано в фазовых системах программного управления.

Известен фазовый дискриминатор, содержащий формирователь импульсов, триггеры, на входы которых поступают сравниваемые сигналы, и логические элементы И Pl).

Указанный фазовый дискриминатор, одна» ко,не обеспечивает ограниченный (+2 Я ) p диапазон преобразования входных сигналов.

Известен также фазовый дискриминатор, содержащий триггеры, на входы которых поданы входные сигналы, и фильтр P2).

Такой дискриминатор не обеспечивает дос- та таточно широкого диапазона преобразования входных сигналов.

Целью изобретения является расширение диапазона преобразования входных сигналов.

Для этого в фазовый дискриминатор вве- ðp дены дополнительные триггеры, цифро-аналоговый преобразователь, и двоичный сумматор, входы которого соединены с выходами

П - разрядных счетчиков, каждый из которых образован оследовательно соединеннвтми 5 триггером и дополнительным триггерами, а выходы — через цифро- аналоговой преобразователь - к входу фильтра.

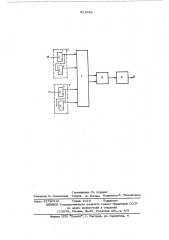

На чертеже показана структурная электрическая схема фазового дискриминатора.

Он содержит триггер 1, соединенный с дополнительным триггером 2, образующие счетчик 3, и триггер 4, соединенный с дополнительным триггером 5, образующие счетчик 6.

Выходы триггеров соединены с соответствующими входами двоичного сумматора 7, выходы которого соединены с входами цифроаналогового преобразователя 8, выход последнего соединен с входом фильтра 9. Входами устройства являются входы 10 и 11 входных триггеров 1 и 4 соответственно, а выходом — выход 12 фильтра 9.

Дискриминатор работает следующим образом.

На входы 10 и 11 подаются входные сигналы импульсной формы, между которыми определяется сдвиг фаз. Счетчики 3 и 6 осуществляют счет поступающих импульсов.

Двоичный сумматор 7 определяет разность кодов счетчиков 3 и 6. При изменении сдви521649 га фаз входных сигналов в пределах 2 tt. на выходе сумматора 7- происходит чередование кодов 00 и 01; в пределах от 2 Г до

4 lt — 01 и 10; в пределах от 4 Я до 67t10 и 11 и т.д. Цифро-аналоговый преобраз ватель 8 преобразует изменения выходных кодов сумматора 7 в широтно-импульсно модулйрованный (ШИМ) сигнал постоянной амплитуды, причем при переходе сдвига фаз входных сигналов с одного периода на дру10 гой пррисходит изменение среднего уровня выходного сигнала цифро-аналогового преобразователя 8 на постоянный уровень, равный амплитуде ШИМ сигнала. Фильтр 9 выделяет постоянную составляющую выходного сигнала преобразователя 8, пропорционален ную сдвигу фаз входных сигналов.

При применении двухразрядных счетчиков

3 и 6 диапазон преобразования дискриминатора равен — 3 1, трехразрядных — + 7

20 и т.д. до + (2 — 1) ТС, где " л " - число разрядов счетчиков. зи в три раз и более увеличить максимальное среднее выходное напряжение устройст ва при неизменном коэффициенте преобразования дискриминатора, что, в свою очередь, позволяет увеличить максимальную скорость подачи привода при сохранении прежней добротности привода по скорости, или при прежней максимальной скорости подачи умень шить коэффициент преобразования дискриминатора, что приводит к снижению требований к величине добротности привода по скорости.

Описанное устройство при использовании в счетчиках 3 и 6 потенциальных триггеров не критично к форме и длительности входных импульсов и надежно работает при переходах от одного периода преобразования разности фаз к другому вследствие независимого счета импульсов двумя счетчиками.

Формула изобретения

Фазовый дискриминатор, содержащий триггеры, на входы которых поданы входные сигналы, и фильтр, отличающийся тем, что, с целью расширения диапазона преобразования входных сигналов, в него введены дополнительные триггеры, цифрс аналоговый преобразователь и двоичный сумматор, входы которого подключены к выходам и — разрядных счетчиков, каждый из которых образован последовательно соединенными триггером и дополнительными триггерами, а выходы — через цифро-аналоговый преобразователь - к входу фильтра.

Источники информации, принятые во внимание при экспертизе изобретения:

1. Авт. св. № 450308, кл. Н 03 2

13/00, 1973 г.

2. Патент Японии 47-12923, кл.

98/53 Е 21 1969 г. (прототип).

Предлагаемый фазовый дискриминатор имеет диапазон преобразования сдвига фаз входных сигналов 3 K и более, что позволяет за счет увеличения фазового сдвига задающего сигнала и сигнала обратной свяТакой дискриминатор может выполнять функцию элемента сравнения, например, по положению приводов подач станков с программным управлением. Тогда на один вход (10) устройства подается импульсный сит нал с системы программного управления, а на другой (11) — импульсный сигнал обрат ЗО ной связи с датчика положения. Разность фаз между входными сигналами, пропорциональная скорости подачи привода, с помощью дискриминатора преобразуется в постоянное напряжение, управляющее приводами З подач.

52 1649

1д (1

Составитель М. Аудринг

Редактор Н. Каменская Техред А. Богдан Корректор Q. Мельниченко

Заказ 4879/516 Тираж 1029 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4