Преобразователь двоичных чисел в двоично-десятичные

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслу6лик

О П И С А Н И Е <>523406

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 01 10.73 (21) 1960306/24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 30.07.76. Бюллетень № 28 (45) Дата опубликования описания 17.09.76 (51) М.Кл а G 06 F 5. 02

Государственный комитет

Совета Министров СССР по делам нзооретений и открытий (53) УДК 681.325 (088.8) (72) Автор изобретения

Я. П. Штурман

Всесоюзный институт научной и технической информации AH СССР (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ

В ДВОИЧНО-ДЕСЯТИЧНЫЕ

Изобретение относится K области вычислительной тех ники .и может быть использовано для преобразования кодов IKBK правильных и смешанных, дробей, так и .целых чисел.

Известны преобразователи двоичных чиср„I,в двоично десятичные, реализующие различные,методы преобразования чисел и обладающие соответственно различным быстродействием.

Один из известных преобразователей осуществляет преобразование последовательного двоичного кода в двоично-,десятичный, опрашивая поочередно десятичные разряды, что при|водит,к циклич|ности его работы и, как следствие, к низкому быстродействию. Кроме этого, он решает ограниченный класс задач (1).

Другой из;известных преобразователей, хотя iH более универсальный, .проводит взаимно-обратные преооразования двоично-десятичных и,двоичных целых и дробных чисел, из-за цикличности функционирования имеет также невысокое быстродействие (2).

Наиболее близи м технпчески м решением к изобретению является преобразователь двоичных чисел,в двоично-десятичные, содержащий блок управления,,вход которого подключен к первой входной шине, первый выход соединен с управляющими входами блока триггеров ы двоично-десяличного шифратора, а второй выход — с переключателем эквивалентов. Выход этого переключателя подключен,к .запоминающему устройспву эк вивалентов десятичных чисел, выход которого свяо зан с первым элементом задержки, выходы блошка триггеров — к первым входам блока элементов «И» и к входам двоично-десятич,ного шифратора, а выходы последнего — к выходной шине. Кроме того, преобразователь в ключает в себя д воичный вычитатель, первый вход которого соединен с,выходом блока элементов «И», второй вход — с первым выходом второго элемента задержки, перзь.й вход которого подключен к второй входнон шине, а второй вход — к выходу двоичного вычитателя (3).

У этого преобразователя также невысокое быстродействие — 10 k циклов, где и — число десятичных разрядов преобразуемого числа.

Цель изобретения — повышение быстродействия преобразователя.

Это достигается тем, что в преооразователь введены блок сравнения и первый и второй формирователи двоичных эквивале ITOB, причем вход первого формирователя двоичных эквивалентов подключен:к входу первого элемента задержки, а выходы — к пер вым входам блока сравнения, второй вход которого связан с управляющим входом блока

ЗО триггеров, третий вход — с вторым выходом

523406

Зо

40 второго элемента задержки, а выходы подсоединены к информационным входам блока ,триггеров. Вход второго формирователя двоичных эквизалентов,соединен с,выходом первого элемента задержки, а,выходы подключены к вторым входам блока элементов «И».

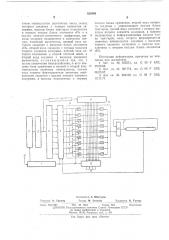

На чертеже представлена блок-схема преобразователя.

Преобразователь содержит блок 1 g;IpalBления, переключатель 2 эквивалентов, запоминающее устройство 8 эквивалентов десятичных чисел, первый формирователь 4 двольчных экВивалентсВ, перзый элемент д 3адсржки, второй формирователь б двоичных эквивалентов, блок 7 сравнеция, блок 8 трл:геров, состоящий из триггеров 9, элементы

«И» 10 блока 11, двои IHo-десятичнь.й шифратор 12, 730HHHûé,âû÷èòàòåëü 18, второй элемент 14 задержки, первую 15 it вторую 1б входные шины, выходную шину 17.

Работает, преобразователь следующим образом.

По входной шине 15 па устройство поступает управляющий,импуль=, запускающий блок 1 управления, .который начинает вырабатывать импульсы, необходимbiå длH автономного функционирования преобразователя.

Одновременно по входной шине 1б Hocле довательно поступает исходное двоичное число А, подлежащее преобразованию. Циркуляцнонный регистр, образованный элементом 14

3 Яде 3>KI

На первый Hzoq cxe t cpasiteHHH б чона 7 в каждом цикле одновременно подаются девять двоичных эквивалентов десятичных чисел вида: В;; = (b; 10 ")э.

Эти э квиваленты вырабатываются формирователем 4 из эквивалентов .вида (10 )„ хранящихся в запоминающем устройстве 8.

Выборкой этих эквивалентов управляет переключатель импульсов. B исходном положении этот переключатель установлен на выборку максимального двоичного эквивалента. Затем ,возбуждаются шины, меньших по алгебраической величине эквиваленто в. Последовательность выдачи эквивалентов определяется значениями k: для правильных дробей — 1; — 2; — 3; ...; — k, для целых чисел А; (lг — 1); (k — 2); ...; О, |для смешанных дробей (1 — 1); ...; 0; — 1; — 2;...; — !.

Применение формирователей позволяет использовать запоминающее устройство 8 меньшей емкости. Она определяется количеством разрядов k преобразованного десятичного числа. В противном, случае ем кость ЗУ необходимо было бы увеличить на порядок.

Во столько же возросло бы и время преобразования.

С помощью блока 7 определяются те двоичные эквиваленты, для которых справедли во

65 неравенство А;) В;;, где 1 — определяет номер десятичного разряда; à L — десятичную цифру (b; = 1, 2, ..., 9).

Блошек 7 для кодов, при которых удовлетворяется указанное услозие, вырабатывает импульсы, поступа|ощие на,информационные входы соответствующих триггеров 9 блоха 8.

Однако прн этом запускается только один, с"мый старший .по весу, триггер, поскольку Выходы блока 7 связаны с запускающими вхо,7ами триггеров 9 того же веса и с запрещающими входами более низких по .весу триггеров.

Тот триггер, который переходит в состоя,ние запуска, подготавливает о .поименный элемент «И» 10 олока элементов «И», ооес:Icчив прохождение через него выбранного двоичного экви ва.7ента В;,, поступающего от формирователя б, полностью идентичного формирователю 4. Необходимая задержка двоичного эквивалента (10 ), до конца цикла, л7ока пе будет известен результат сравнения, осуществляется элементом 5 за.7ержки. Выбранный "-,квивалент В,; удовлетворяет приведенному условию, следовательно, операция ,Вычитания из его числа А (а далее — пз частичной разности А;),Возможна. Вычитание осуществляется с помощью одноразрядного двои . .о;о вычитателя 18.

Сигналы соответствующе.-о триггера блока

8 поступают также .и на двоичпо-десятичный шифратор 12, осуществляющий .påoopаaoaaние десятичного кода цифры в двоич ю-десятичный код тетрады, снимаемой с выходной шипы,17.

Указанные преобразования повторяются 3 последующих ци клах, в результате которых формируются очередные тетрады преобразуемого числа. При этом возможны два случая: .преобразование за канчивается через k циклов (по чИслу k десятичных разрядов); преобразование заканчивается раньше, а именно в том цикле, каK только блок сравнения зафиксирует равенство кодов А, = В;;.

Введение в схему преобразователя двух формирователей двоичных эквивалентов и блока сравнения выгодно отличает предлагаемый преобразователь двоичных чисел в двоично-десятичные от указанного прототнпа, так ка к уменьшается необходимое кол...ество циклов прес бразовакия (в 10 раз). В результате, возрастает быстродействие рассматриваемого устройства.

Формула изобретения

Преобразователь двоичных чисел в двоично-десятичные, содержащий блок управления, вход;которого подключен к первой .входной шине, первый выход соединен с управляющими входами блока триггеров и двоично-десятичного шифратора, а второй, выход подключен к переключателю эививалентов, выход которого соединен с запоминающим устрой523406

Составитель А. Шкатулла

Техред М. Семенов

Редактор !4. Грузова

Корректор В. Гутман

Заказ 833/1067 Из д Мо 1543 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета й1инистров СССР по делам изобретений и открытий

Москва, К-35, Раушскаи наб., д. 4/5

Тип. Харьк. фил. пред. «Патент» ством эквивалентов десятичных чисел. выход которого соединен с первым элементом задержки, выходы блока триггеров подключены к:первым входам блока элементов «И» и к входам двоичпо-десятичного шифратора, выходы которого подключены к,выходным шинам, двоичный вычитатель, первый вход которого соединен с выходом олока элементов

«И», второй вход соединен с первым выходом второго элемента задержки, первый вход которого,подключен к второй входной шине, а второй вход соединен с выходом двоичного вычитателя, о тл ич а ю щ ий с я тем, что, с целью увеличения быстродействия, в него введены блох .сравнения и первый и второй формирователи двоичных эквивалентов, причем вход первого формирователя двоичных эквивалентов соединен с входом первого элемента задержки, а выходы подключены к первым входам блока сравнения, второй вход которого соединен с управляющим входом блока триггеров, третий вход соединен с.вторым выходом, второго элемента задержки, а выходы подключены к информационным входам блока триггеров, вход второго формирователя двоичных эквивалентов соединен с выходом первого элемента задержки, а выходы подключены IK вторым входам блока элементов

«И», 1

Источеики информации, принятые во внимание при экспертизе.

1. Авт. св. № 225551, кл. G 06 F 5/02, 15 29 08 68

2, Авт. св. М 201774, кл. G 06 F 5/02, 0,8. 09. 67.

3. Авт. св. № 296102, кл. G 06 F 5/02, 12. 1 1.71.