Устройство для параллельного суммирования двух чисел

Иллюстрации

Показать всеРеферат

я 1ентно-тмхическяи бнчрдотен,„, OllHCAHHE

ИЗОБРЕТЕНИЯ п11523452

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 14.08.74 (21),2052842/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.07.76. Бюллетень № 28

Дата опубликования описания 28.09.76 (51) М. Кл. G 11С 11/02

Государственный комитет

Совета Министров СССР (53) УДК 681.327.02 (088,8) по делам изобретений и открытий (72) Авторы изобретения В. Г. Колосов, Н. И. Колосова, В. Ф. Мелехин и В, В. Талдыкин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯ

ДВУХ ЧИСЕЛ

Изобретение относится к вычислительной технике и может быть применено в цифровых устройствах и системах, имеющих магнитное запоминающее устройство (МОЗУ).

Известны устройства для параллельного суммирования двоичных чисел с последовательной реализацией переносов на магнитном оперативном запоминающем устройстве с линейной выборкой.

В одном из таких устройств в качестве логического блока используются специально выделенные линейки МОЗУ. Однако для суммирования т-разрядных двоичных чисел оно требует от пяти до 2 — Зт циклов обращения к

МОЗУ (1).

Наиболее близким техническим решением к изобретению является устройство для параллельного суммирования двух чисел, содержащее накопитель магнитного оперативного запоминающего устройства, блоки формирования импульсов записи, выход каждого из которых подключен к входу считывания следующего блока формирования импульсов записи, блок усиления воспроизведения, выходы которого через коммутирующие элементы соединены с входами записи блоков формирования импульсов записи, а входы — с выходами блоков формирования импульсов записи и выходами накопителя магнитного оперативного запоминающего устройства, управляющие входы коммутирующих элементов — с выходами блока управления, и блок формирования стробирующих импульсов, выход которого связан с управляющим входом блока усиления воспроизведения (2).

Это устройство имеет большое количество элементов задержки, что обусловливает сложность и низкое быстродействие устройства.

Цель изобретения — упрощение устрой10 ства и повышение его быстродействия.

С этой целью выходы блока усиления воспроизведения через коммутирующий элемент соединены с входами считывания блоков формирования импульсов записи, а управляющий

I5 вход коммутирующего элемента — с выходом элемента «И», первый вход которого связан с выходом блока формирования импульса от спада входного сигнала, Вход последнего подключен к выходу блока формирования стро20 бирующих импульсов, второй вход элемента

«И» — к выходу блока управления.

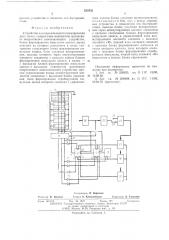

На чертеже показана схема устройства.

Она включает в себя накопитель МОЗУ, организованный по системе 2Д. Накопитель

25 МОЗУ 1 состоит из двух блоков: универсального 2 и функционального 3. Универсальный блок 2 содержит большую часть ячеек, адресные шины которых подключены к выходам дешифратора адреса, а функциональный блок

30 3 — ячейки 4 — 8, адресные шины которых под523452

50 а,Vb,;

55 бО

Е, -= Р,5;1,/Р, /3, б5 соединены к реверсивным ключам. В ячейках

4 — 8 выполняются поразрядные логические функции «И», «ИЛИ», «НЕ». Разрядные шины 9, общие для обоих блоков 2 и 3 накопителя МОЗУ, соединены с входами блока 10 усиления воспроизведения, а также с выходами 11 блоков 12 формирования импульсов записи, Блоки формирования импульсов записи выполняют также функцию регистра числа (регистра регенерации) . В качестве таких блоков могут служить, например, магнитно-транзисторные элементы, использующие для запоминания магнитные сердечники с прямоугольной петлей гистерезиса. Блок формирования импульсов записи имеет входы записи 13, 14 и считывания 15, 16. Вход 13 блока 12 формирования импульсов записи -го разряда подключен через диод 17 к выходу i-го разряда блока 10 усиления воспроизведения, а с другой стороны входы 13 всех разрядов — к коммутирующему элементу 18. Вход 14 i-ro разряда через диод 19 подсоединен к выходу (i — 1) -го разряда блока 10, и с другой стороны входы 14 — коммутирующему элементу 20. Вход 16 считывания i-го разряда через диод 21 подключен к выходу (i — 1) -ro разряда блока 10, с другой стороны входы 16 — к коммутирующему элементу 22. Вход 15 блока формирования импульсов записи -го разряда соединен с выходом 11 аналогичного блока (1 — 1) -ro разряда. Управляющий вход коммутирующего элемента 22 связан с выходом элемента «И» 23, вход 24 которого подключен к выходу блока

25 формирования импульса от спада входного сигнала, вход блока 25 — с выходом блока

26 формирования стробирующих импульсов, соединенным также с управляющим входом блока 10 усиления воспроизведения. Управляющие входы коммутирующих элементов 18, 20, блока 26, а также вход 27 элемента «И»

23 подсоединены к соответствующим выходам блока управления, не показанного на чертеже.

Суммирование двух двоичных чисел в предлагаемом устройстве выполняется за пять обращений к МОЗУ по следующему алгоритму: ввод числа а в специально выделенные для выполнения логических операций линейки

МОЗУ; ввод числа b в те же линейки с получением выражений вычисление слова переносов Р;+1 по формуле

,- = (as V У Ыт Рг) (1) вычисление 5 по формуле

S; =-= а, Vb \,/а,б„(2) где $„— предварительная сумма без учета переносов; вычисление суммы "; по формуле

1О

2О

2,5

3О

4О

Рассмотрим работу предлагаемого устройства при образовании слова переносов по формуле (1) в третьем цикле обрящсшгя к накопителю согласно приведенному алгоритму.

Перед началом третьего цикла слово а, Ч а; записано в ячейках 4 и 5 функционального блока 3 накопителя МОЗУ 1, а слово a b, в ячейках 6 и 7. В первом такте третьего цикла проводится считывание ячейки 4. Одновременно возбуждается блок 26 формирования стробирующих импульсов и открывается коммутирующий элемент 20. Поскольку на вход

27 элемента «И» 23 сигнал не поступаот, то элемент 22 остается невозбужденным. На выходах блока 10 усиления воспроизведения появляется считанное слово

a„V b;. Со сдвигом на один разряд влево через диоды оно записывается в блоки формирования импульсов записи.

Во втором такте третьего цикла происходит считывание ячейки 6. Одновременно возбуждается блок 26 формирования стробирующих импульсов и подается снгпял па вход 27 элемента «И», От спада стробнрующего импульса блок 25 формирует импульс на выходе, который поступает на вход 24 элемента «И» 23, на выходе последнего образуется импульс, возбуждающий элемент 22. Таким образом, элеMcIIT 22 возбуждается с задер>ккой, равной длительности стробирующего импульса. На выходах блока 10 усиления воспроизведения появляется считанное слово а;6;. В момент

»cl V1I IK3tl&I5f элемента 22 KOQ O IH I HlfltOI о слова со сдвигом на один разряд влево через диоды

21 поступает на входы 16 считывания блоков

12, При этом те блоки 12 формирования импульсов записи, на входы 16 которых поступил импульс, формируют на выходе 11 импульс записи, так как в первом такте в них была записана «единица» кодом a; V b,. Выходной импульс блока формирования импульсов записи

1г-го разряда считывает блок формирования импульсов записи следующего (/г+1)-го разряда. Таким образом, возбуждается волна переноса. Код на выходах 11 соответствует слову переносов Р;+1., вычисленному по формуле (1). Импульсы записи с выходов 11 поступают в разрядные шины 9 накопителя

МОЗУ 1. Одновременно формируются импульсы адресных токов записи в ячейках 4 и

8, в результате чего слово переносов записывается в эти ячейки.

Длительность импульсов тока в адресных шинах должна быть больше длительности импульсов тока в разрядных шинах на величину максимальной задержки распространения волны переноса от младшего разряда до старшего. Задержка считывания блоков формирования импульсов записи во втором такте, обеспечиваемая блоком 25, необходима д.гя того, чтооы HcK;Ilo÷èòü влияние помех и разрядных шинах 9 от импульсов записи на работу блока 10 усиления воспроизведения. Осуществление необходимой задержки с помощью блоков

25, 23, связанных с блоком 26, позволяет уп523452

Формула изобретения

Составитель В, Березкин

Тсхрсд А, Камышникова

Корректор А. Галахова

Редактор И. Грузова

Заказ 18-13/!0 Изд, U o 1572 Тираж 723 I1îдписное

I1I IIIIII II I Государственного комитета Совета Министров CCCP но делам изобрстсннш п отк1нятнй

113035, Москва, )K-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2 ростить устройство и повысить его оыстродейстнис, Устройство для параллельного суммирования двух чисел, содержащее накопитель магнитного оперативного запоминающего устройства, блоки формирования импульсов записи, выход куя(дого из котоpых подl(.1ючс1I к l3Uочу считывания следующего блока формирования импульсов записи, блок усиления воспроизведения, выходы которого через коммутирующие элементы соединены с входамп записи блоков формирования импульсов записи, а входы— с выходами блоков формирования импульсов записи и выходами накопителя магнитного оперативного запоминающего устройства, причем управляющие входы коммутирующих элементов соединены с выходами блока управления, блок формирования стробирующих импульсов, выход которого соединен с управляющим входом блока усиления воспроизведения, отл и и а ю щесся тем, что, с цслью упрощения устройства и повышения его быстродействия, выходы блока усиления воспроизведения через коммутирующий элемент соединены с входами считывания блоков формирования импульсов записи, а управляющий вход коммутирующего элемента соединен с выходом элемента «И», первый вход которого соединен

I0 с выхо1ом блока формирования импульса от спада входного сигнала, вход которого соединен с выходом блока формирования стробирующих импульсов, второй вход элемента «И» подключен к выходу блока управления.

Источники информации, принятые во внимание при экспертизе.

1. Лвт. св. № 226955, кл. G 11F 15/00, 20 16,09,68, 2. Лвт. св. № 268498, кл. G 11С 11/02, 10.04.70 (прототип) .