Динамическая ячейка памяти

Иллюстрации

Показать всеРеферат

Все о

li и3!снтиО-т»"

I библи!те! . " +

ОПИСАНИЕ „„ЫЗаь@

ИЗОБРЕТЕН ИЯ

Сок!з Советских

Социалистических

Республик .

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено- 11.06.74 (21) 2033851/24 (51) М. Кл. G 11С 11/40 с присоединением заявки К

ГосУдаРственный комитет (23) Приоритет

Совета Министров СССР (53) УДК 681.327 66 (088.8) Опубликовано 30,07.76. Бюллетень М 28

Дата опубликования описания 28.09.76 ло делам изобретений

» ч открытий (72) Авторы изобретения

А, И. Стоянов и В. С. Хорошуиов (71) Заявитель (54) ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯ1 И

Изобретение относится к области электроники и вычислительной техники и может быть испол!.зовано в производстве интегральных запомипающи. устройств для цифровы«вы !ислитсл!.пы«мт!и!ин.

Известны динамические ячейки памяти, содержащие два МДП-транзистора. В этих ячейках памяти считывание производится с разрушением хранимой информации. Этот недостаток устранен в динамической ячейке памяти, содержащей два МДП-транзистора и запоминающий конденсатор, В ней стоки первого и второго транзисторов подключены кразрядной шине, исток первого транзистора и первая обкладка запоминающего конденсатора— к затвору второго транзистора, вторая обкладка запоминающего конденсатора подсоединена к первой адресной шине, затвор первого транзистора — к второй адресной шине, а исток второго транзистора — к первой адресной шине.

Недостатками известной ячейки памяти явля!Отся малое время «ранепия информации и низкое быстродействие в режиме считывания.

Г1ервый из указанных недостатков обусловлен тем, что запомипак>щий конденсатор не может быть заряжен до напряжения, превышающего пороговое напряжение второго транзистора. так как в режиме хранения этот транзистор открыт и через него связаны разрядная шина и первая адресная шина, что делает невозможным считывание из соседней ячейки. Второй недостаток объясняется возрастанием в процессе считывания напряжения на разрядной

5 шине, уменьшением напряжения затвор — исток транзистора считывания, что приводит, следовательно, к уменьшению тока считывания.

Кроме того, так как перед считыванием разрядная шина разряжается до нулевого потен1п циала, то емкость ее велика и время заряда разрядной шины до величины, необходимой для считывания, также велико.

Цель изобретения — увеличение времени хранения информации и повышение быстро15 действия ячейки в режиме считывания.

Это достигается тем, что в ячейке исток второго транзистора подключен к второй адресной шине.

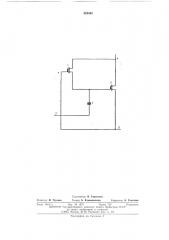

На чертеже представлена схема ячейки па20 мяти, где 1 — первый транзистор; 2 — второй транзистор; 3 — запоминающий конденсатор;

4 - —; 5 — первая адресная шина; б — вторая адресная шина.

Ячейка памяти может работать в режима«

25 хранения, считывания, записи н регенерации информации.

В режиме хранения информации возможны два состояния элемента: первое — запоминающий конденсатор 3 разряжен до нуля, вто30 рое — запоминающий конденсатор заряжен

523454

5э до напряжения U (2U„oð, где U> — напряжение на запоминающем конденсаторе; U>

Перед считыванием разрядная шина 4 заряжается до высокого уровня напряжения Е)

ЗУ„р, а при считывании величина напряжения на ней должна быть больше U»p с тем, чтобы исключить проводимость транзисторов

2 соседних ячеек, имеющих общую с выбранной разрядную шину 4 в том случае, когда запоминающие конденсаторы их заряжены.

В режиме считывания информации на адресную шину 6 подается нулевой уровень напряжения, а на адресную шину 5 — уровень напряжения, соответствующий пороговому

U„„. При этом транзистор 1 остается закрытым, а состояние транзистора 2 определяется состоянием запоминающего конденсатора. Если запоминающий конденсатор был разряжен, то напряжение на затворе транзистора 2 недостаточно для протекания тока через него и он остается закрытым. Если же запоминающий конденсатор был заряжен, то напряжение на затворе транзистора 2 превышает пороговое, транзистор 2 открывается, и через него происходит разряд шины 4. Информация распознается по состоянию транзистора 2 — открыт или закрыт, причем независимо от изменения напряжения на разрядной шине 4 напряжение на затворе транзистора 2 остается постоянным.

В режиме записи информации на шину 5 подается уровень напряжения, соответствующий У„,ч„а на шину 6 — высокий уровень напряжения L)3U„, открывающий транзистор 1. При этом для записи логического нуля на разрядную шину поступает уровень напряжения, соответствующий U„», и конденсатор

3 разряжается через открытый транзистор 1.

Для записи логической единицы на разрядную шину подается уровень напряжения, соответствующий ЗЬ „„р, конденсатор 3 заряжается до напряжения величиной 2У„„р.

По окончании цикла записи на шину 6 поступает уровень напряжения, соответствующий

U,.„транзистор 1 закрывается и элемент переходит в режим хранения.

Регенерация информации осуществляется в следующем порядке: сначала считывание информации и определение состояния элемента, а затем запись считанной информации обратно в ячейку.

Новая динамическая ячейка памяти выгодно отличается от указанного прототипа.

В предлагаемой ячейке памяти запоминающий конденсатор заряжается до напряжения, равного 2У„,р, чем увеличивается время хранения информации (или период регенерации).

Кроме того, улучшены условия считывания, так как при считывании напряжение на затворе второго транзистора не меняется, поэтому по мере разряда разрядной шины ток считывания не уменьшается, а остается постоянным. Заряд разрядной шины перед считыванием до высокого уровня напряжения обеспечивает малую емкость разрядной шины, что также приводит к уменьшению времени считывания, Наконец, в запоминающем элементе возможно применение как обычного конденсатора, так и конденсатора типа «бикап».

В последнем случае снимаются ограничения на амплитуду сигнала, подаваемого на первую адресную шину при считывании, так как когда «бикап» разряжен, его емкость мала, а входная емкость второго транзистора велика.

B результате сигнал считывания не передается на затвор второго транзистора. При заряженном «бикапе» его емкость велика, и сигнал считывания приложен к затвору второго транзистора. Таким образом, предлагаемая ячейка памяти позволяет существенно увеличить время хранения информации и повысить быстродействие в режиме считывания.

Формула и",îáðåòåíèÿ

Динамическая ячейка памяти, содержащая два МД П-трап",èñòoðà и запоминающий конденсатор, стоки первого и второго транзисторов подключены к разрядной шине, исток первого транзистора и первая обкладка запоминающего конденсатора подключены к затвору второго транзистора, вторая обкладка запоминающего конденсатора подключена к первой адресной шине, а затвор первого транзистора — к второй адресной шине, отл и ч аю ща я ся тем, что, с целью увеличения времени хранения информации и повышения быстродействия в режиме считывания, в ней исток второго транзистора подключен к второй адресной шине.

523454

Составитель В. Гордонова

Техред А. Камышникова

Редактор И. Грузова

Корректор А, Галахова

Т««огра< «я, «р. Са«у«ова, 2

Заказ 1843, 11 Изд, Ма 1572 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий! 13035, Москва, )K-35, Раушская «аб., д, 4 5