Интегральное запоминающее устройство

Иллюстрации

Показать всеРеферат

опНСАНМЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< ц 523455

Сова Советских

Социалистических

Республик (61) Дополнительное к авт, свид-ву (22) Заявлено 04.10.74 (21) 2065674/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.07.76. Бюллетень № 28

Дата опубликования описания 03.12.76 (51) N Кл.з G 11C 11/40

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

А. И. Мальцев, А. П. Нагин и Ю. P. Чернышев (71) Заявитель (54) ИНТЕГРАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в запоминающих устройствах цифровых вычислительных машин.

Известно интегральное запоминающее устройство (ЗУ), содержащее накопитель, ячейки памяти которого содержат МДП-транзисторы с изменяемым порогом включения, и дешифраторы (1). Известное устройство имеет низкое быстродействие и требует высоких входных уровней напряжения при записи информации.

Наиболее близким к изобретению является интегральное запоминающее устройство, содержащее матричный накопитель, каждая ячейка памяти которого содержит последовательно включенные МДП-транзистор с изменяемым порогом включения и вентильный

МДП-транзистор, затворы вентильных МДПтранзисторов каждой строки подключены к соответствующим выходам дешифратора строк, истоки вентильных МДП-транзисторов— к выходной шине через МДП-транзисторы выборки, затворы которых подсоединены к соответствующим выходам дешифратора столбцов, затворы МДП-транзисторов с изменяемым порогом включения — к управляющей шине, шину питания и:шину нулевого потенциала (2).

Недостатками этого устройства являются низкое быстродействие при считывании чз-за малой крутизны нагрузочного транзистора и повышенная мощность рассеяния при записи вследствие статического характера работы ячеек памяти при записи.

Цель изобретения — повышение быстродействия и уменьшение рассеиваемой мощности интегрального запоминающего устройства.

Для этого устройство содержит дополнительну.ю управляющую шину, а каждая ячейка па10 мяти дополнительный вентильный МДП-транзистор и емкостный элемент, стоки МДП-транзисторов с изменяемым порогом включения через дополнительные вентильные МДП-транзисторы, затворы которых подключены к уп15 равляющей шине, к,шине питания и одному из электродов ем костного элемента, другой электрод которого подсоединен к шине нулевого потенциала.

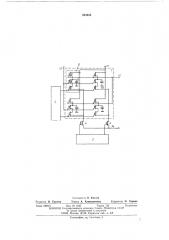

На чертеже представлена схема устройства.

20 Запоминающее устройство содержит м атричный накопитель 1, дешифратор 2 строк, дешифратор 3 столбцов, МДП-транзисторы 4 выборки, ячейки 5 памяти, МДП-транзисторы

6 с изменяемым порогом включения, вентиль25 ные МДП-транзисторы 7, дополнительные вентильные МДП-транзисторы 8, емкостные элементы 9, шину 10 нулевого потенциала, шину

11 питания, дополнительную управляющую шину 12, управляющую шину 13 и выходную

30 шину 14.

523455

Запись информации в запоминающее устройство проводится за два цикла. В первом цикле осуществляется стирание информации, хранимой в ячейках 5 памяти. Для этого на шину 11 питания, дополнительную управляющую шину 12 и выходную шину 14 подается нулевой потенциал, а на управляющую шину

13 — высокий потенциал.

В результате пороги всех МДП-транзисторов 6 с изменяемым порогом включения становятся высокими.

Во втором цикле напряжение подается на шину 11 питания и дополнительную управля|ощую шину 12, а на выходную шину 14 поступает нулевой потенциал. При этом дополнительные вентильные МДП-транзисторы открываются и емкостные элементы 9 заряжаются до уровня напряжения на шину питания. После заряда емкостных элементов 9 напряжение подается на управляющую шину 13. В выбранной с помощью дешифратора 2 строк и дешифратора 3 столбцов ячейке памяти вентильный МДП-транзистор 7 открывается, и емкостный элемент 9 разряжается, при этом в МДП-транзисторе 6 с изменяемым порогом включения порог включения уменьшается.

При считывании на шину 11 питания, управляющую шину 13, дополнительную управляющую шину 12 подаются напряжения через ячейку памяти, выбранную с помощью дешифратора 2 строк и дешифратора 3 столбцов, ток протекает в выходную шину 14, если порог включения этой ячейки низок; в противном случае ток в выходной шине отсутствует.

Таким образом, величина тока в выходной шине 14 соответствует информации, хранимой в выбранной ячейке памяти.

Предложенное интегральное запоминающее устройство выгодно отличается от прототипа тем, что в цепи считывания нет нагрузочных транзисторов и в режиме записи ячейки памяти работают в динамическом режиме. В результате этого увеличивается быстродействие при считывании и снижается рассеиваемая мощность при записи.

Формула изобретения

Интегральное запоминающее устройство, содержащее матричный накопитель, каждая

10 ячейка памяти которого содержит последовательно включенные МДП-транзистор с изменяемым порогом включения и вентильный

МДП-транзистор, затворы вентильных МДПтранзисторов каждой строки подключены к

15 соответствующим выходам дешифратора строк, истоки вентильных МДП-транзисторов подключены к выходной шине через МДПтранзисторы выборки, затворы которых подключены к соответствующим выходам дешиф20 ратора столбцов, затворы МДП-транзисторов с изменяемым порогом включения подключены к управляющей шине, шину питания и шину нулевого потенциала, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и

25 уменьшения рассеиваемой мощности, устройство содержит дополнительную управляющую шину, а каждая ячейка памяти — допол нительный вентильный МДП-транзистор и емкостный элемент, причем стоки МДП-транзисто30 ров с изменяемым порогом включения через дополнительные вен тильные МДП-транзисторы, затворы которых подключены к управляющей шине, шине питания и одному из электродов емкостного элемента, другой элек35 трод которого подключен к шине нулевого потснци ал а.

Источники информации, принятые во внимание при экспертизе:

40 1. Патент США № 374403 6, кл. 340 — 173, 1973.

2. Авт. св. № 458036, G 11 С 11/40, 19.07.73.

523455

Составитель В. Фролов

Техред А. Камышникова

Корректор О. Тюрина

Редактор И. Грузова

Типография, по. Сап иова, 2

Заказ 2899/4 Изд, № 1545 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5