Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ш1523456

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сове Ссеетсиик

Социалистическик

Ресвублии (61) Дополнительное к авт. свид-ву (22) Заявлено 19.11.74 (21) 2076497/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.07.76. Бюллетень № 28

Дата опубликования описания 11.08.76 (51) М. Кл. G 11С 17/00

Государствеииый комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 628.327.66 (088.8) 1

Л. О. Ваганян, А. М. Иванов, М. М. Момджян и Л. Ж.,Хдспарян--.- ..", (72) Авторы изобретения (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области цифровой вычислительной техники и автоматики и может быть использовано в запоминающих устройствах цифровых вычислительных машин.

Известны постоянные запоминающие устройства, содержащие адресный дешифратор и накопитель, который для хранения каждого бита информации содержит отдельный запоминающий элемент (1).

Из известных постоянных запоминающих устройств наиболее близкими по технической сущности являются постоянные запоминающие устройства, содержащие адресный дешифратор и накопитель, каждый выходной разряд которого содержит по два запомни ающих элемента, и блок распознавания выходных сигналов (2J

Целью изобретения является упрощение устройства.

Указанная цель достигается тем, что блок распознавания выходных сигналов в каждом разряде содержит выходной элемент ИЛИ и сумматор по модулю два, причем первый вход выходного элемента ИЛИ подключен к выходу первого элемента памяти данного разряда, второй вход выходного элемента ИЛИ подключен к выходу сумматора по модулю два, первый вход которого подключен к выходу второго элемента памяти данного разряда, а второй вход — к вы; îäó сумматора по модулю д|ва предыдущего разряда. В первые элементы памяти всех разрядов записываются одиночные единицы, а во вторые — первые единицы групп подряд расположенных единиц и первые нули, расположенные после последней единицы группы.

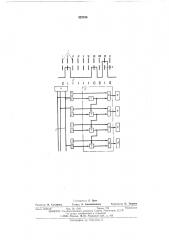

На чертеже приведены пример прошивки одного десятиразрядного слова, хранимого в запоминающем устройстве, и схем а постоян10 ного запоминающего устройстга, хранящего четырехразрядные слова.

В первые элементы 1 памяти всех разрядоз

1 — Х и во вторые элементы 2 памяти заведены связи адресной шиной 3 в соответстгии с ко15 дом 0111110010. В первый элемент 1 памяти разряда 1Х заведена связь, что соответствует хранению одиночной единицы. Связи, заведенные во вторые элементы памяти разрядов 11 и Ч11, соответствуют хранению первой единицы группы подряд расположенных единиц и первого нуля, расположенного после последней единицы этой группы.

Постоянное запоминающее устройство состоит также из дешифратора 4 адреса, кото25 рый адресными шинами 3 подключен к первым элементам 1 памяти и вторым элементам

2 памяти блока 5 распознавания выходных сигналов, который в каждом разряде содержит выходной элемент ИЛИ 6 и сумматор 7

З0 по модулю два. Причем выход сумматора 7

523456 подключен к входу выходного элемента ИЛИ 6 данного разряда и выходу сумматора 7 следующего разряда. Выходы вторых элементов 2 памяти подключены к входам сумматоров 7 соответствующих разрядов, а выходы первых элементов 1 памяти — к входам выходных элементов ИЛИ 6, выходы которых подключены к триггерам 8 регистра числа.

Устройство работает следующим образом.

Дешифратор 4 возбуждает одну из адресных шин 3, которая в соответствии с программой записи подключена к элементам 1 и 2 памяти. В разрядах, где записаны одиночные единицы, на выходах элементов 1 памяти появляется сигнал, который через выходной элемент ИЛИ 6 устанавливает триггер 8 регистра числа в состояние «1».

В разрядах, где записаны первые единицы групп и первые после группы единиц нули, сигнал, появившийся на выходе элементов 2 памяти, поступает на вход сумматора 7, другой вход которого соединен с выходом сумматора 7 предыдущего разряда. Если на одном из входов сумматора 7 появится сигнал (что соответствует разрядам, где должны храниться единицы групп), то триггер 8 регистра числа соответствующего разряда установится в положении «1».

Если сигналы появляются сразу на обоих входах сумматора 7 (что соответствует разряду, где хранится первый по порядку нуль после группы подряд идущих единиц), то на выходе сумматора 7 сигнал не появится и триггер 8 данного разряда останется в нулевом состоянии.

На чертеже первой (левой) адресной шиной

3 запяса н код 111.1,,второй шиной 3 — код 0100 и последней шиной 3 в код 1110.

Формула изобретения

1р Постоянное запоминающее устройство, содержащее адресный дешифратор, накопитель, каждый разряд которого содержит два элемента памяти, и блок распознавания выходных сигналов, отличающееся тем, что с

15 целью упрощения устройства, блок распознавания выходных сигналов в каждом разряде содержит выходной элемент ИЛИ и сумматор по модулю два, причем первый вход выходного элемента ИЛИ подключен к выходу первого элемента памяти данного разряда, второй вход выходного элемента ИЛИ подключен к выходу сумматора по модулю два, первый вход которого подключен к выходу второго элемента памяти данного разряда, а второй вход — к выходу сумматора по модулю два предыдущего разряда.

Источники информации, принятые во внимание при экспертизе:

ЗО 1. Брик Е. А, Техника ПЗУ, «Советское радио», 1973 г.

2. Авт. св. № 385317, кл. G 11 С 17/00, 22. 04. 71 r.

523456

0 i 1 I 1 0 0 I 0

Составитель Е. Брик

Техред А. Камышникова

Корректор О. Тюрина

Редактор Н. Суханова

Типография, пр, Сапунова, 2

Заказ 1835/19 Изд. М 1545 Тираж 723 Подписное

Ц1-!ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Я-35, Раушская наб., д. 4/5