Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

1 и!

О П И С А Н И Е (ii) 523457

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Соаиалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 26.05.75 (21) 2138784/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.07.76. Бюллетень № 28

Дата опубликования описания 11.08.76 (51) М. Кл, С 11С 29/00

G 06F 11/00

Государствеиный комитет

Совета министров СССР (53) УДК 681.327.6 (088.8) ао делам изобретений и открытий (72) Автор изобретения

И. М. Соколов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известны устройства для защиты памяти (1, 2, 3).

Одно из известных устройств для определения границ защитной зоны содержит только один регистр с записью в нем общих разрядов для всех запрещенных адресов (1). Это устройство может быть использовано только для защиты памяти небольшого объема.

В другом из известных устройств действительный адрес образуется путем сложения относительного адреса и оазисной константы (2).

Такое устройство не обеспечивает высокой скорости работы.

Из известных устройств для защиты памяти наиболее близким техническим решением к изобретению является устройство для защиты памяти, содержащее регистр адреса страниц, подключенный к дешифратору страниц, регистр маски страниц, выходы которого соединены с одними входами элементов «И» первой группы, другие входы которых подключены к выходам дешифратора страниц, а выходы — к входам основного элемента «ИЛИ», элементы «И» второй группы, дешифратор строк и регистр адреса строк (3).

В этом устройстве для защиты памяти невозможно записывать выполняемую программу в произвольные участки памяти, так как для каждой программы необходимо формировать количество адресов, соответствующее целому числу страниц, хотя в одной из страниц программы может быть использовано всего одно слово, что приводит к неэкономнчному использованию дорогостоящей памяти и снижению надежности устройства.

Цель изобретения — повышение надежности устройства за счет возможности защиты лю1р бого участка памяти.

Это достигается тем, что предложенное устройство содержит дополнительные элементы

«И» и «ИЛИ» и запоминающий блок. Адресные входы запоминающего блока подсоеди15 иены к выходам элементов «И» первой груп пы, а выходы — к одним входам элементов

«И» второй группы, другие входы которых через дешифратор строк подключены к выходам регистра адреса строк, а выходы через дополнительный элемент «ИЛИ» — к одному входу дополнительного элемента «И», другон вход которого соединен с выходом основного элемента «ИЛИ».

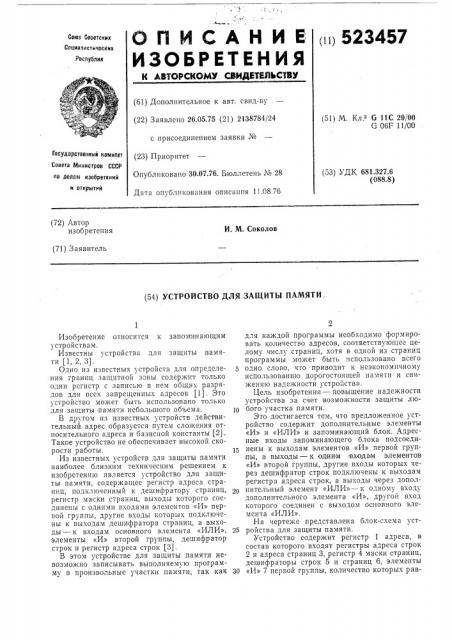

На чертеже представлена блок-схема уст25 ройства для защиты памяти.

Устройство содержит регистр 1 адреса, в состав которого входят регистры адреса строк

2 и адреса страниц 3, регистр 4 маски страниц, дешифраторы строк 5 и страниц 6, элементы

30 «И» 7 первой группы, количество которых рав523457 но числу страниц, основной элемент «ИЛИ» 8, элементы «И» 9 второй группы, число которых равно количеству строк в странице, а выхолы подключены к адресным шинам 10

Кроме того, в устройство введены запоминающий блок 11 для хранения масок строк и дополнительные элементы «ИЛИ» 12 и «И»

13. Адресные входы блока 11 подсоединены к выходам элементов «И» 7, а выходы — к одним входам элементов «И» 9, другие входы которых через дешифратор 5 строк подключены к выходам регистра 2 адреса строк, а выходы — к одному входу элемента «И» 13, другой вход которого соединен с выходом элемента

«ИЛИ» 8.

Работает устройство следующим образом.

Перед началом работы в регистр 4 вводится код маски страниц, используемых в заданной программе, а в блок 11 — коды всех строк, используемых в заданной программе.

Далее после формирования адреса в регистре 1 происходит сравнение на элементах «И»

7 информации,,поступающей из дешифратора

6 страниц и из регистра 4 маски страниц. При совпадении информации на входах одного из элементов «И» 7 формируется адрес страницы памяти, по которому происходит, выбор также кода маски всех строк для этой страницы из блока 11. Этот код маски строк сравнивается с информацией, поступающей из дешифратора 5 строк. В случае совпадения информации на входах одного из элементов «И» 9 формируется адрес строки. При наличии адреса строки и адреса страниц на выходе элемента «И» 13 образуется сигнал разрешения обращения к памяти. Когда нет адреса строки или адреса страницы, на выходе элемента

«И» 13 появляется сигнал, запрещающий обращения к памяти, вырабатывающий сигнал на прерывание выполнения программы. Пр .t этом (как и после выполнения полностью заданной программы) регистр 2 адреса строк, регистр 3 адреса страниц, регистр 4 маски страниц и блок 11 устанавливаются в нулевое состояние (цепи установки на чертеже не показаны), Предложенное устройство может быть использовано для адресации с защитой большого объема памяти. При этом необходимо в него дополнительно ввести регистр адреса блока, дешифратор блока, регистр маски блока, элементы «И» и «ИЛИ» со связями, аналогичными описанным (но без подключения к блоку 11).

Введение в устройство для защиты памяти

5 блока 11, элементов «И» 13 и «ИЛИ» 12 позволяет записывать выполняемые программы (имеющие разную длину) в произвольные участки памяти. Это приводит к экономичному использованию дорогостоящей памяти ЦВМ. Так, 10 например, для реализации двадцати программ в предложенном устройстве необходимо формировать в 1,5 раза меньше адресов (строк) и соответственно иметь в 1,5 раза меньше объем .памяти LtBM по сравнению с известным

15 устроиством (3)

Формула изобретения

20 Устройство для защиты памяти, содержащее регистр адреса страниц, подключенный к дешифратору страниц, рагистр маски страниц, выходы которого соединены с одними входами элементов «И» первой группы, другие вхо25 ды которых:под ключены к выходам дешифратора стра ниц, а выходы — к входам основного элемента «ИЛИ», элементы «И» второй группы, дешифратор строк и регистр адреса стирок, отличающее.ся тем, что, с целью

30 повышения на детности устройства, QIBO содержит дополнительные элементы «И» и «ИЛИ» и запоминающий блок, адрес ныевходы которого подключены к выходам элементов «И» первой группы, а выходы — к одним входам эле35 ментов «И» второй группы, другие входы которых через дешифратор строк подключены к выходам регистра адреса строк, а выходы через дополнительный элемент «ИЛИ» — к одному входу дополнительного элемента «И», 40 другой вход которого соединен с выходом основного элемента «ИЛИ».

Источники информации, принятые во вни45 мание при экспертизе:

1. Патент США № 3264615, кл. 340 †1.

5, 1966.

2. Авт. св. № 230519, М., кл. G 06 F 11/00, 1967.

50 3. Дроздов Е. А. и др. Многопрограммные

LIBM, Воен. издат., М., 1974, стр. 324 — 326.

523457

Редактор И. Грузова

Корректор О Тюрина

Заказ 1835/20 Изд. № 1545 Тираж 723 Подписное

Ц1-1ИИПИ Государственного комитета Совета Министров СССР по делам изобретепий и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, нр, Сапунова, 2

Г

1 б

Составитель В. Рудаков

Техред А. Камышникова