Система для синтеза тестовых сигналов

Иллюстрации

Показать всеРеферат

тсюа (оветсних

Соци ааистичес:. их пт >)ии (11) " "4X5 1

Е АВТОРСХОМУ СВИДЕТЕЛЬ< ;: ВУ

Ф+ г> ь (61} Дополнительное к авт. свид-ву (22) Заявлено 30,01.75(21) 2101041/24 с присоединением заявки № (23) Приоритет, (51) М. Кл.

С 06 F 11/00

Государственный комитет

Совета Министров СССР по делам иэооретений н открытий (43) Опубликовано05.08.76.бюллетень _#_ 28 (53) У! К 681 326 .7 (088.8) (45) Дата опубликования описания 15.12.76 (72) Автор изобретения

Б. Г. Сергеев

Институт электронных у 1равляюшпх ь!ашин (71) Заявитель (54) СИСТЕМА ДЛЯ СИНТЕЗА ТЕСТОВЫХ СИГНАЛОВ

25 изобретение относится к вычислительной те лыке и, в частности к систе:1ам аввЂ.оматического синтеза тестов контроля раоо-.оспособности и диагностики неисправностей слогкньгх цифровых объектов, узлов, áëо1(ов;! устройств средств вычислительной технип и и автоматики, построенных kIQ интег;-.аль; ых схе:;!ах.

Известны системы, содергкап;ие 11ВМ.> соединеннуго двусторонними связями с блоко:,i сопрягкения, регистр входного век-;ора, выход которого соединен со входо;.! образца ооьекта, а вход через коммутатор подкл;очен к блоку сопрягкения, устройства коммутации, соединенные с соответству1оц1и:ли входа. Iii u вь ходами образца объекта.

> !ля современных цифровых объектов разработка тестов, облада1оших гарантирова>iной полнотой (т.е. способностью обнаругкивать заданный класс неисправностей объектов) или заданной точностью диагностики является черезвычайно слогкной задачей.

Известные системы автоматизации решения этой задачи могкно разделить на две категории.

K первой категории от 1осятся систе.. ikk> цэлико;! базирующиеся на универсальпьх

ЦВМ общего н.значения и не содергкашие каких-лцоо специальных аппаратных средств.

В таких систе..1ах задачи, связанные с создание.» тестов, реша1отся на стандартном оборудовании UBN c по!(ошь.3 соответству.:ошего комплекса программ. Наиболее эф!)ж;!т!1в!1ые;>1етоды синтеза тестов:= использованиеги подобных систе:. основыва:отея

:.,"-. програм1 !по:.! модепированип зада>и!ого объекта Ор ивсехегомопификаций 0,>Ох> О>( соответствуюших неисправностям 1, 2,..., К псевдослу>ikàéíbiõ BxogHbix послепова: еЛЬНОСтяХ, раССХ1атрПВаЕМЬ)1Х Ках ПетопцИалиные тестl-Ii Ь и посл)едоватепы1ост1! Гепериру-ются специал!.ной программой, и каждая

ИЗ ПИХ r(ПРИКЛаДЫВаэтСЯ КО ВХОДа)г.i К!ОДЕ лей обьективов го, 0,... 0 а>

В результат" .,юдел .ровапия этих объекTDB на последовательности + вычисляются их выходные реакции у, у ... у

i 1 о> на эту последовательност т

P«k(ii !" Y Уе,..., $ сравг!1!ва1отся с к реакцией 1 с целью составления списка о те 11еис|1рав".О-сти l, ÷II:-tûå выбираются из

ОЗУ 10);

Об11;ее управлени процессо. l синтеза теста, составле.|ие списков неисправностей, обнаруживаемых каждой из исследуемых входных последовательностей, вывод тестов и других данных.

Перед начало::л работы комплексу програ;лм LlBM 7 задается исходная ипфор.. мация, определяющая объект, для которого производится построение тестов. Зта информация вкл|очает: перечень типов интегральных схем объекта с указанием, какая из этих схем подключена к каждому процессору 9; перечень всех входов объекта, входов синхронизации, входов установки в исходное состояние (в символических или физических адресах выходов регистра 3; входную последовательность приведения объекта в исходное состояние и последовательность сигналов цикла синхронизации, Кроме того, машина должна содержать заранее введенные библиотечные данные, в †.ом числе модели (моделируюшие програм,лы) всех типов интегральных схем, списки их наиболее вероятных неисправностей, данные, характеризу|ошие контрольную аппаратуру и, вчастности,,возможные законы фор лирования псевдослучайных входных последовательностей и т.д.

Работа системы начинается с загрузки моделирующих программ в ОЗУ 10 процессоров 9, соответствующих тем типам интегральных схем, которые подключены с помощью стройств 8 к этим процессорам.

Эти программы извлекаются организующей программой из attetttttei - мяти ЦВМ и

1 B,М передаются через шины связи 5 и регистры

12 процессоров в ОЗУ 10. После загрузки программ в ОЗУ засыпаются данные, модифицирующие эти программы в соответствии с типами неисправностей интегральных схем на которых будет исследоваться входная последовательность, рассматриваемая как возможный тест эбьекта.

В моделирующую программу каждого процессора вводятся одновременно Г нелсправностей (;де J — разрядность слова

ОЗУ 10). Таким образом, программа каждого процессора эбеспечиьает параллельное моделирование 1 модификаций интегральной схемы, соответствующих Г ее различным неисправностям. Организующая программа системы обеспечивает приложение кэ входам объекта 1 последовательности приведения объекта в исходное состояние.

В каждом такте Ф этой последовательности система работает следующим образом. Входной сектор, соответствуюшии такту, передается L(BM 7 через блэк сопряжения 6 и кэммутатэр 4 ь эсгистр 3, чтэ эбесtleч11вает ttpttitolêeítte этэгэ вся эра кэ входам объекта 1. Пэ окончании переходных процессов в объекте ЦВМ 7 с помощью сигналов, передаваемых пэ шинам связи 5, запускает выполнение мэделирую— ших программ в процессорах 9.

Каждый процессор 9 работает автономно, независимо от других, под управлением прэ1п граммы, находящейся в его ОЗУ 10. B начале выполнения программы каждого процессора значения сигналов, установившиеся на входах интегральной схемы объекта 1, с которой связан данный процессор, считывают ся с помощью блока 18 в регистр 15 и далее через регистр 12 записываются в ОЗУ

10. Зти значения сигналов рассматрива|этся как -начения входов моделей интегральной схемы. На основании этих значений входов

20 и состояния в такте Ф-1 моделирующая программа вычисляет состояние всех элементов каждой модели. Вычисление строится как итеративный процесс. Он считается законченным, если состояние элементов каждой

25 модели оказывается неизменным в двух следующих одна за другой итерациях. Конец выч|лсления фиксируется индикатором 19 процессора, по сигналу которого блок 13 управления сигнализирует ЦВМ 7 об окончанил

З0 выполнения его программы. По окончании

Выполнения моделиру|Ощих про1-рамм Все|ли процессорами 9 системы организующая программа ЦВМ 7 подготавливает вектор входной последователы|ости, соответствующий

Зэтакту 4 +1, и описанный процесс повторяется.

По окончании приложения последовательности приведения объекта в исходное состояние образец объекта 1 эказываетсл в известном начальном состоянии. В сэответ0ствующее начальное состояние приводятся также модели интегральных схем, реализуемые программами процессоров 9 (если в эти модели не внесены неисправности, то эни находятся в том же состоянии„ чтэ и =-ээтветствуюшие интегральные схемы ооъекта).

Затем LlBM 7 начинает процесс генерирования и исследования входных последОВательнэстей, расс латриваям1э|х В еа» честве возможных тестов. При этом ".àáîòà

50 системы В каждом такте 4 л|эбои такои последовательности скдадывается из описан1|ых действий, Выполняемых В такте Ф последовательности приведения объекта в исход ное состояние, и ряда дополнителы|ых.,гоп олнитель ными действиями л р оцесс оров 9 явля|отся сравнение полученных в результате вычисления значений выходов моделеи интегральных схе|л, преобразованных в состВотстВин с типами проверяе|лых неис|1равнэ6 стей, с фактическими значения|,itI выходных

524181 с блоком сопря>кения и с соответствуюшим

ОЗУ.

Кроме того, каждый процессор системы содержит регистры адреса и данных, блок управления, подключенные к шине связи с

ОЗУ, и счетчик команд, выход которого соединен с первым входом регистра адреса.

Выход регистра данных подключен к первым входам буферного регистра, блока коммутации, регистра кода операции, блока выполне-10 ния логических операций, входу счетчика команд и второму входу регистра адреса.

Второй вход блока коммутации соединен со входом процессора выход — со вторым входом буферного регистра, соединенного дву- 15 сторонними связями с блоком выполнения логических операций, выход которого подключен ко входу индикатора окончания моделирования и к первому входу дешифратора результатов, второй вход которого и соот- 20 ветствуюший вход регистра данных соедине-. ны с выходом буферного регистра. Выходы регистра кода операции, индикатора окончания моделирования, дешифратора результатов и дешифратора адреса процессора под- 25 ключены к соответствуюшим входам блока управления. Вход дешифратора адреса процессора, второй вход регистра кода операции и соответствующие входы и выходы регистра данных и блока управления подклю- 30 чены к шине связи с блоком сопряжения.

Для данной системы время Ò анапиза одного такта теста определяется формулой

35> т.е. в п раз меньше, чем для известных систем синтеза первой категории, и в и раз меньше, чем для системы второй категории для приведенного ранее примера 40 объекта 7 -- 0,03 сек. При этом система позволяет моделировать любые логические неисправности внутренних элементов интегральных схем объекта и не требует для синтеза тестов специально приспособленных 45 образцов объектов. Система применена при синтезе тестов для синхронных объектов, допускаю щих внешнюю синхронизацию, конструкция которых предусматривает возможность подключения соответствуюших контактных уст- 50 ройств к внешним выводам интегральных схем. Никаких других ограничений на схему и конструкшпо объекта не накладывается.

Тесты, получаемые с помощью данной 55 системы, рассчитаны на применение совместно с любой контрольной аппаратурой, обеспечивающей подачу тестов на входы объектов контроля, считывание логических значений сигналов с выходов всех интеграль- о ных схем объекта и сравнение этих значений с эталонными значениями, заданным" в программе контроля или получаемыми от эталонного образца объекта.

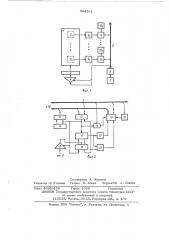

На фиг. 1 приведена блок-схема системы; на фиг. 2 — блок-схема специализированного процессора.

Система содержит образец объекта 1; интегральные схемы Ъ вЂ”, регистр 3 входного вектора, — коммутатор 4, шины 5, вязи, блок 6 . опря>кения 1JBM 7, устройства коммутации 8 - 8 специализированные процессоры 9 - 9 и ОЗУ 10 - 10к.

Специализированный процессор содер>кит регистр 11 адреса, регистр 12 данных, блок

13 управления, счетчик 14 команд, буферный регистр 15, регистр 16 кода операций блок 17 логических операций, блок 18 коммутации, индикатор 19 окончаний моделирования, дешифратор 20 результатов и дешифратор 21 адреса процессора.

Регистр 3 входного ве.стора предназначен для запомипания и приложения ко входам объекта 1 сигналов, соответствующих текушему такту исследуемой входной последовательности. С помошью коммутатора 4 обеспечивается последовательно-параллельный прием данных в регистр 3 с шин сопряжения с ЦВМ машиной.

Каждый процессор 9 служит для моделирования соответствуюшей ему интегральной схемы 2 объекта 1 (с учетом имитируемых неисправностей этой схемы) с помошью программы, хранимой в соответствующем данному процессору ОЗУ 10.

Система работает следу:ошим образом.

Вместе с соответствующим комплексом программ IJBM 7 обеспечивает выполнение следуюших управляющих функций в системе: генерирование входных последовательностей, испытываемых в качестве возможных тестов для заданного ш фрового объекта; приложение входных, последовательностей и сигналов синхронизации ко входам объекта (через коммутатор 4 и регистр 3); загрузку моделирующих программ в ОЗУ

10 (через шины связи 5 и соответствуюшие узлы процессоров 9); модификацию моделирующих программ в соответствии с типами проверяемых неисправностей интегральных схем объекта; запуск процессора 9 в каждом такте проверяемой входной последовательности для выполнения моделирующих программ; обнаружение момента окончания работы моделируюших программ в каждом такте и накопление. в ОЗУ машины данных, определяюших все обнаруживаемые в текушем так524181 к/О

om 8

Составитель А. Жеренов

Редактор Л. Утехина Техред И. Ковач Корректор A. Лакида

Заказ 4995/432 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

524181 сигналов интегральных схем объекта и получение данных о том, какие из моделируемых неисправностей обнаруживаются в текущем такте. С этой цепью по окончании моделирования программа, выполняемая каждым процессором, считывает состояние выходов связанной с процессоров интегральной схемы объекта и сравнивает его:с вычисленными значениями выходов 1- моделей, Если для какой-либо из v моделируемых неисправностей вычисленные значения не совпадают со считанными значениями, то программа фиксирует номер этой неисправности. Пс окончании описанных действий процессор сигнализирует UBN 7 об окончании выполнения программ в такте 4 . После того, как эти сигналы получены от всех процессоров системы, организующая программа производит выборку из ОЗУ данных о всех неисправностях, которые обнаруживаются в текущем такте, и помещает их в список обнаруживаемых неисправностей, соответствующий исследуемой входнойпоследовательности. Затем программа — генератор входных последовательностей образует вектор, соответствующий такту +1, и система описанным выше способом переходит к проверке этого такта выходной последовательности. После того как исследуемая последовательность закончится либо в некотором ее такте в список обнаруживаемых неисправностей войдут все неисправности моделируемой группы, организующая программа производит засылку в

ОЗУ 10 данных, модифицирующих моделирующие программы в соответствии с новой гругпой неисправностей. Затем производится приложение к объекту 1 последовательности приведения в исходное состояние и на1 пинается исследование генерируемой входной последовательности (с первого ее такта) для новой группы неисправностей. При этом работа системы аналогична работе, описанной для предыдущей группы неисправностей.

Применение данной системы позволяет создавать эффективные тесты с требуемой полнотой и диагностической способностью для объектов, построенных на больших интегральных схемах.

Система легко может быть реализована на модулях. При использовании для построения системы известных больших интегральных схем каждый процессор и соответствующее ему ОЗУ могут быть реализованы в виде одной печатной платы, имеющей унифицированное соединение с шинами связи блока сопряжения с ЦБМ. При такой реализации обеспечивается возможность гибкого изменения состава (числа процессоров и

ОЗУ) в зависимости от числа интегральных схем в объектах, для которых должны синтезироваться тесты.

Ф ормула изобретения

1. Система для синтеза тестовых сиг10 налов содержащая I«BM, соединенную двусторонними, связями с блоком сопряжения, регистр входного вектора, выход которого соединен со входом образца объекта, а вход через коммутатор подключен к блоку сопря15 жения устройства коммутации, соединенные с соответствующими входами и выходами образца объекта, о т л и ч а ю ш а я— с я тем, что, с целью повышения быстродействия системы путем параллельного моделирования неисправностей всех устройств объекта, она содержит специализированные процессоры и оперативные запоминающие устройства. (ОЗУ), причем вход каждого специализированного процессора подключен к выходу соответствующего устройства коммутации каждый специализированный процессор соединен двусторонними связям- с блоком сопряжения и с соответствующим запомина:сшим устройством.

30 2. Система по и. 1, о т л и ч а ющ а я с я тем, что специализированный процессор содержит регистры адреса и данных, блок управления, подключенные и шине связи с ОЗУ, счетчик команд, выход которо35 ro соединен с первым входом регистра адреса; выход регистра данных подключен к первым входам оуферного регистра, блока коммутации, регистра кода операции, блока выполнения логических операций,ко входу счетчика ко40 манд и ко второму входу регистра адреса, второй вход блока коммутации соединен со входом специализированного процессора, выход — с вторым входом буферного регистра, соединенного двусторонними связями с бло45 ком выполнения логических операций, выход которого подключен ко входу индикатора окончания моделирования и к первому входу дешифратора результатов, второй вход которого и соответствуюшийвход регистра данных соединены с выходом буферного регистра; выходы регистра кода операции, индикатора окончания моделирования, дешифратора результатов и дешифратора адреса процессора подключены к соответствующим входам блока управления; вход дешифратора адреса процессора, второй вход регистра кода операции и соответствующие входы и выходы регистра данных и блока управления подключены к шине связи с блоком сопряжения.