Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е () д 4 Р4

ИЗОБРЕТЕН ИЯ

К АВТОРО4ОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистииесних

Реслублин (61) Дополнительное к авт свид-ву(22) Заявлено 14,03.75 (21) 2113648/24 с присоединением заявки № (23) Приоритет(51) М. Кл

G 11 С- 11/00

Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (43) ()публиковано05.08.76.Бюллетень № 29 (53) УДК 681.327.67 (088.8 ) (45) Дата опубликования описания 20.10.76 (72) Авторы изобретения

Е. П. Балашов, А. Ю. Гордонов, Н, В. Ерхова, E. B. Коленов, Г, A. Петров, B. С. Степанов и Ю. А, Суровцев (71) Заявитель (54 ) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к ЗУ и может быть использовано, в частности для кодирования и декодирования информации.

Известны логические ЗУ (1, 2„3) пассивного (1), и активного типа f23. Однако в таких устройствах нельзя проводить кодирование и декодирование информации.

Наиболее близким техническим решением к данному изобретению является логическое

ЗУ, содержащее дешифратор, соединенный с 1о регистром адреса и -разрядным блоком памяти, регистр слова, управляюшие блоки, подключенные к блоку памяти, и управляюшие шины (.31.

Однако это устройство не позволяет ко- 15 дировать и декодировать информацию, 11елью изобретения является расширение функциональных возможностей устройства за счет выполнения в нем кодирования и декодирования информации. 20

Поставленная цель достигается тем, что предложенное устройство содержит элементы "И" и "NJM" и триггер. Первый вход

i -го разрядного элемента "ИЛИ" (1 — 1, 2,..., т ) подключен к выходу 1 -го эпемен- 25 та "И" первой группы, один вход которого соединен с первой управляюшей шиной, а другой - с х -ым выходом регистра слова, Второй вход i -го разрядного элемента

"ИЛИ", кроме т -го, подключен к выходу (i + 1)-го элемента "И второй группы, один вход которого соединен со второй шиной управления, а другой — с (1 + 1 ) -ым выходом регистра слова, Третий вход i -го разрядного элемента "И.ПИ", кроме первого, подключен к (1 — 1)-му элементу "И" третьей группы, один вход которой соединен с третьей управляюшей шиной, а другой с (1 — 1) -ым выходом регистра слова. Выходы разряднь:х элементов "ИЛИ" подключены к соответствующим входам блоков управления. Выходы регистра слова подключены через первый элемент "ИЛИ" к одному входу первого элемента "И", другой вход которого соединен с четвертой управляюшей шиной, а выход — с одним из входов элемента "ИЛИ", выход которого соединен со входом триггера, а другой вход — с выходом второго элемента "И".

Входы второго элемента "И" подключены

524224 соответственно к пятой управляющей шине и первому выходу регистра слова.

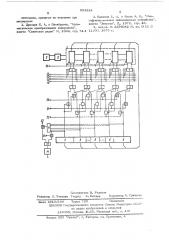

На чертеже изображена блок-схема предложенного усгройства.

Устройство содержит и -разрядный блок

5 памяти 1, дешифратор 2, регистр адреса 3, управляющие блоки 4, разрядные элементы

"ИЛИ" 5, элементы "И" 6 первой группы, используемые при записи, элементы "И 7

l0 второй группы, используемые при сдвиге информации влево, эле менты И 8 третьей группы, используемые при сдвиге информации вправо, регистр слова 9, первый элемент "И" 10,первый элемент "ИЛИ" 11, второй элемент И 12, N второй элеменг "ИЛИ" 13, триггер 14, служащий для анализа состояния разрядов регистра 9. Устройство содержит также управляющие шины 15-25.

Первый вход i -го элемента "ИЛИ" 5 подключен к выходу i -го элемента "И" 6, один вход которого соединен с первой управляющей шиной 21, а другой - с 1 -ым выходом регистра 9, второй вход,i -ro элемента "ИЛИ" 5, кроме т -го, подключен к выходу (i + 1)-го элемента "И" 7, один вход которого соединен со второй шиной управления 22, а другой — с (i + 1)-ым выходом регистра 9. Третий вход 1 -го элеменга "ИЛИ" 5, кроме первого, подклю- 3Q чен к (— 1)-му элементу "И" 8, один вход которого соединен с третьей управляющей шиной 20, а другой с (1 — 1)-ым выходом регистра 9.

Выходы элементов "ИЛИ" 5 подключены 35 к соответствующим входам блоков 4, выходы регистра 9 через элемент "ИЛИ" 11— к одному входу элемента "И" 10, другой вход которого соединен с четвертой управляющей шиной 23, служащей для анализа 4О содержимого разрядов регистра 9 " на нуль", а выход — с одним из входов элемента "ИЛИ"

13, выход которого соединен с входом триггера 14, а другой вход — с выходом элемента "И" 12. Входы элемента "И" 12 подклю-35 чены соответственно к пятой управляющей шине 24, служащей для анализа содержимо"о первого разряда регистра 9 "на нуль", и первому выходу регистра 9.

Для кодирования и декодированияинформа-щ ции, например, в циклическом коде с исправлением одной ошибки устройство должно выполнять набор следующих операций: "логический сдвиг влево", "логический сдвиг вправо", "сумма по модулю два", "анализ 55 содержимого регистра слова на нуль", "анализ содержимого первого разряда регистра слова на нуль".

Рассмотрим работу устройства при операции " логический сдвиг влево". В исход- 6О ном состоянии на регистре адреса 3 хранится произвольный адрес ячейки А блока памяти 1, а на регистре слова 9 — операнд

Х. При подаче управляющего сигнала на шину 22 сигнал поступает на элементы "И" 7, При этом информационные сигналы с выходов триггеров регистра слова 9 через элементы "И" 7 и элементы "ИЛИ" 5 поступают на блоки 4. Одновременно управляющие сигналы поступают на шины 16, 18 и 19, и при подаче сигнала на шину 15 в ячейку

A. блока памяти 1 записывается код опе) ранда Х со сдвигом влево на один разряд.

Предложенное устройство позволяет кодировать и декодировать информацию, что значительно расширяет его функциональные возможности.

Формула изобретения

Логическое запоминающее устройство, содержащее дешифратор, соединенный с регистром адреса и т: -разрядным блоком памяти, регистр слова, управляющие блоки, подключенные к блоку памяти, управляющие шины, о тл и ч а ю щ е е с я тем, что, с целью расширяriH функциональных возможностей устройсгва, оно содержит элементы "И" и

"ИЛИ итриггер; первыйвход i -горазрядного элемента "ИЛИ" (; = 1,2,..., и.) подключен к выходу i -го элемента "И" первой группы, один вход которого соединен с первой управляющей шиной, адругой-с 1 ым выходом регистра слова; второй вход 1 -го разрядного элемента "ИЛИ", кроме с -го, подключен к выходу (+ 1)-го элемента "И" второй группы, один вход которого соединен со второй шиной управления, а другой — с (1 + 1)-ым выходом регистра слова; третий вход -1-о разрядного элемента "ИЛИ", кроме первого, подключен к (1 - 1 )-ому элементу "И" третьей группы, один вход которой соединен с третьей управляющей шиной, а другой с (i — 1)-ым выходом регистра слова; выходы разрядных элементов "ИЛИ" подключены к соответствующим входам блоков управления; выходы регистра слова подключены через первый элемент

"ИЛИ" к одному входу первого элемента

"И", другой вход которого соединен с четвертой управляющей шиной, а выход — с одним из входов второго элемента "ИЛИ", другой вход которого соединен с выходом второго элемента "И" и входом триггера; входы второго элемента "И" подключены соответственно и пятой управляю пей шине и первому выходу регистра слова, 524224

Составитель В, Рудаков

Редактор Л. Утехина Техред А, Богдан Корректор A. Гриценко

Заказ 491О/399 Тира:к 723 Подписное

ЫНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент", г. Ужгород, ул, Проектная, 4Источники, принятые во внимание при экспертизе:

1. Дроздов Е. А. и Пятибратов, "Автоматическое преобразование информации", изд-во Советское радио" М. 1964, crp. 74.5

2. Балашов Е. li. и Кноль А. И., "Многофункциоы льные запоминаюшие устройства", изд-во "Энергия"., Л„1972, crp. 46, 3. Авт,св, ¹ 2259042 М. кл. G ll С

11/ОО, 1975 г.