Устройство для вычисления квадратного корня

Иллюстрации

Показать всеРеферат

Союз Советских

Социал истииеских

Республик

О П И С А Н И E !!!!в !оат

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 28.10.74 (21) 207148О 24 (51) М, Кл.

Ст06 ;" 7/38 с присоединением заявки ¹ (23) 11риоритет тосудасетоенный комитет

Совета тй1;нистров СССР по делам изобретений и открыт!!й (43! O!"Ó Л11ковано15 08 G.Б!Оллетень ¹30 (53) уды 681 8О5 . 5 (088.8),. (45) Jalа Опубликования описания 1,.11,76

A. В. 2вдэк!1мэ.З> B„P!. Жариков, Л. Б, Кап;!ан, J. Э. Крейндлин и B. С. Хайкэв (72) Авторы изобретения (7!) Заявитель (-4) у -- 1-О! С ВО Ъ. .! БЫЧИС, 1Н," 1 КВл1;1=у,—, -Ор К0 - НЯ

Изобретение относится к Вычислите II-ной технике и предназна тено для использования В Вычислительн1 !х ма!ц!1!!ах, раоэта!Огцих В реальном ма! !штабе Времени.

Известны устройства для Вычисления

1 квадратного корня I „,cîäàpæèöl.с регистрры,сумматоры накопите! Вно -o типа, счетчик циклов, логические элементь! и схемы сдвига до rn разрядов Вкл!Очитет!ьнэ. 3> таких устройствах используется асинхронный алl Оритм I.o3Bo !Нкш!Iй д Iя !екотооь!х ко» дэВВ1х сочстаний -!Олкср -.ннОГО Выражения достичь сун!ественного пэвыгцения бь ст=9пействия. Однако, для цег:oro ряда кодов эффективность этого алгоритма значительно снижается и в пред=.ло О=ICIpодейсгвие указанных устроиств может раВняться быстоо действ!Но устройств, использу!Огцих синхронные (с жестко зафиксированным длч требуемой точности числом Гцагоь вычисления) ал! Оритмь!. Кроме тoгэ, для этОГО алГОритма суцтествует !1еобхэд!!! !Ость ачализа групп разрядов остатка, чгэ приводит к дополнительному расходу оборудования, и, как следс гв !е, счиженик надежности и технслоги 1носг.". усгро!1ства В целом.

Ыаибс !эе близким чо технической съ!цности к !1ан!!Ому !1зобретен!НО яьляеся усгГ . 1 ройгтво L ), использ ч!Оццее синхронный алгоритм и сэдер!Канте сумматор-нaKCHптель, реги<..тр, триггер, регистр сдвига результата, блок управления, два элемен Ià и, Выход регистра соединен с перв.-пн входом сумматора-накопителя, выход которо! О соединен со входом триггера, вь!ход которого соединен с первым входом блока управления, с первым Входом первого элемента И, с первь!м входом второго элемента И и Вторь!м входом сумматора-накопителя, третий вход которогэ сэединен с выходом блока управления, второй вход кэтэрого соединен с выходом регистра сдвига везультата. Схема такого устройства срав.нительно сложна и, следовательно, велики аппарат урные затрат ы.

1(ель изэоретения — упроцгение устроиства.

Это достигается те!1, что устройство сэдержит блок коррекции, первый выход Ко525G87 торого соединен со вторым входом второго элемента И, выход которого соединен с четвертым входом сумматора-накопителя, пятый вход которого соединен со вторым выходом блока коррекции, а шестой вход сумматора-накопителя соединен с третьим выходом блока коррекции и вторым входом первого элемента И, выход которого соединен со входом регистра сдвига результата. 10

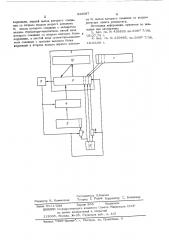

На чертеже изображена схема устройства.

Устройство содержит регистр 1, сумматор-накопитель 2, регистр 3 сдвига результата, блок управления 4, триггер 5 — и блок коррекции 6, элементы И 7, 8.

Сумматор-накопитель 2 состоит из комбинационного сумматора 9 и накопителя

1 G„9 предназначен для работы с числами лредставленными в дополнитель- 29 ном коде. Режим работы сумматора определяется состоянием триггера 5 знакового разряда. Выход триггера 5 подключен к управляющим входам блока управления 4 и цепи переноса в младший разряд сумматора И

9.

Нулевое состояние триггера 5 для комбинационного сумматора 9 соответствует режиму "Вычитание . В этом случае код вычитаемого при прохождении через блок 30 управления 4 инвертируется, а в цепи переноса в младший разряд комбинационного сумматора 9 формируется сигнал наличия переноса. -сли триггер 5 находится в состоянии "1", что соответствует для комбинационного сумматора 9 режиму "Суммирование", то через блок управления 4 на комбинационный сумматор поступает прямой код второго слагаемого и на входе младшего разряда комбинационного сумматора 9 40 сигнал переноса отсутствует.

Перед началом вычисления подкоренное выражение находится в регистре 1. Накопитель 10, регистр 3 сдвига результата и триггер 5 обнуляются, а в блок коррекции

6 заносится код 111. В соответствии с этим в первом шаге вычислений осуществляется режим "Вычитание".

Два младших разряда уменьшаемого поступают на вход комбинационного сумматора

9 из двух старших разрядов регистра 1, на остальные разряды поступает информация с накопителя 10 со сдвигом на два разряда влево, Обратный код вычитаемого передается в сумматор с регистра сдвига результатов и с младшего разряда блока коррекции 6, информация с двух других его разрядов подается в сумматор без инвертирования. Результат вычисления фиксируется в накопителе 10. По окончании первого шага вычислений выполняется сдвиг содержимого регистра 1 на два разряда влево, а регистра сдвига результата 3— на один разряд влево, при этом в младший разряд регистра 3 через блок управления

4 заносится содержимое старшего разряда блока коррекции 6, после чего этот разряд обнуляется и до окончания вычислений в блоке коррекции 6 хранится постоянный код

011. В триггер 5 заносится информация со знакового разряда комбинационного сумматора 9. С этого момента устройство готово к выполнению второго шага вычислений, Далее выполнение операции в каждом шаге сводится к следующему: передача содержимого накопителя 10 в комбинационный сумматор 9 со сдвигом на два разряда влево, в два разряда записывается информация из двух старших разрядов регистра 1 соответственно; передача в сумматор содержимого регистра сдвига результата 3 и блока коррекции 6; суммирование (вычитание) запись результата суммирования (вычитания) в накопитель 1О, а информации из знакового разряда комбинационного сумматора 9 на триггер 5; сдвиг содержимого регистра 1 и 3, при этом в младший разряд регистра 3 заносится очередной разряд результата.

По окончании последнего шага вычислений в регистре сдвига результата находится результат вычислений.

Использование данного изобретения позволяет упростить схему устройства и, следовательно, аппаратурные затраты при его производстве.

Формула изобретения

Устройство для вычисления квадратного корня, содержащее сумматор-накопитель, регистр, триггер, регистр сдвига результата, блок управления, два элемента И, выход регистра соединен с первым входом сумматора-накопителя, выход которого соединен со входом триггера, выход которого соединен с первым входом блока управления, с первым входом первого элемента И, с первым входом второго элемента И и вторым входом сумматора-накопителя, третий вход которого соединен с выходом блока управления, второй вход которого соединен с выходом регистра сдвига результата, отличающееся тем, что, сцелью упрощения устройства, оно содержит блок

525087

Составитель Л.Каплан

Те хред Г. Родак Корректор С, Болдижар

Редактор Н. Каменская

Заказ 5111/588 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал "ППП "Патент", г. Ужгород, ул. Проектная, 4 коррекции, первый выход которого соединен со вторым входом второго элемента

И, выход которого соединен с четвертым входом сумматора-накопителя, пятый вход которого соединен со вторым выходом блока коррекции, а шестой вход сумматора-накопителя соединен с третьим выходом блока коррекции и вторым входом первого элемен6 та И, выход которого соединен со входом регистра сдвига результата.

Источники информации, принятые во внимание при экспертизе:

1. Авт. св. % 435522 кл. Ci06 7/38, 05,07.74 г. т ca 239665,кл C,(t

18.03.69 г.