Малая управляющая цифровая вычислительная машина

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено17.01.75 (21) 2100009/24 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.08.76.Бюллетень № 30 (45) Дата опубликования описания 09.12.76

Союз Советских

Социалистимеских

Республик (») 525C99 (51) М.. Кл. б 06 У 15/20

Государственный нанитет

Совета Министров СССР па делан изооретений и открытий (53) УДК

681.325 (088.8) И. В. Прангишвили, Е. В. Бабичева, А. В. Вейц, Я. А. Левертов, В. Д. Малюгин, Д. В. Певцов, Э. Г. Прохорова, В. В. Соколов, М. А. Ускач и А. И. Шкатулла (72) Авторы изобретени (71) Заявитель

Ордена Ленина институт проблем управления АН СССР (54) МАЛАЯ УПРАВЛЯЮЩАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ

МАШИНА

Изобретение относится к вычислительной технике, в частности к малым управляющим цифровым вычислительным машинам, предназначенным для решения задач управления в реальном масштабе времени и различного рода вычислительных задач.

Известен цифровой процессор, содержащий постоянное запоминающее устройство команд, счетчик команд, блок контроля и арифметико- логический блок, информационный выход которого соединен с первыми: информационными входами блока управления памятью и устройства ввода-вывода, при этом первый информационный вход арифметико-логического блока соединен с первым информационным выходом блока управления памятью и вторым информационным входом устройства ввода-вывода, а второй информационный вход соединен с первым информационным выходом устройства ввода-вывода и вторым информационным входом блока управления памятью, третий, четвертый, пятый и шестой информационные входы zoторого соединены соответственно с выходами оперативного запоминающего устройства и первого, второго и третьего регистров памяти, второй информационный BbIxoA блока управления памятью соединен со входами оперативного запоминающего устройства и первого, второго и третьего регистров памяти, а первый управляющий вход соединен с первым выходом регистра команд, первый вход которого соединен с первым выходом постоянного, запоминающего устройства

10 программ.

Известное устройство характеризуется невысоким быстродействием, обусловленным необходимостью обмена между отдельными логическими устройствами при вы олнении

l5 произвольной машинной команды, и низким коэффициентом использования оборудования.

Целью изобретения является увеличение быстродействия и повышение коэффициента использования оборудования. В описываемой

20 машине это достигается тем, что арифметико-логический блок выполнен на однородной перестраиваемой структуре и введены олок. управления, блок настройки и блок формирования макрокоманд, выход которого

25 соединен со вторым управляющим входом

525099 блока управления памятью, а вход — со вторым выходом регистра команд, второй вход которого соединен с первым выходом постоянного запоминающего устройства команд, а третий выход подключен к первому управляющему входу устройства ввода-вывода, второй информационный выход которого подключен к первому входу блока управления, а второй информационный вход соединен с первым выходом блока контроля, первый 10 вход которого соединен с контрольным выходом блока управления памятью, а второй и третий входы подключены соответственно к контрольному выходу блока настройки и первому выходу блока управления, второй вход которого соединен со вторым выходом блока контроля, третий вход блока управления соединен со счетчиком команд, а четвертый вход подключен к первому выходу блока настройки, второй выход блока управления соединен с постоянным запоминающим устройством программ, второй выход которого подключен к третьему управляющему входу блока управления памятью, третий выход блока управления соединен с первым входом постоянного запоминающего устройства команд, второй вход которого подключен ко второму выходу блока настройки, а второй выход соединен с первым управляющим входом арифметико-логического блока, управляющий выход которого соединен со счетчиком команд, а второй управляющий вход подключен к третьему выходу блока настройки, вход которого соединен с четвертым выходом блока управления.

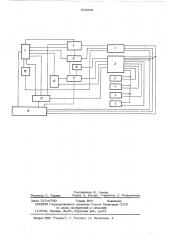

На чертеже представлена структурная схема описываемой машины.

Она содержит арифметико-логический

40 блок 1, выполненный на однородной перестраиваемой структуре, оперативное запс минающее устройство 2, блок управления памятью 3, первый 4, второй 5 и третий

6 регистры памяти, блок управления 7, 45 постоянное запоминающее устройство команд 8, блок настройки 9, постоянное запоминающее устройство программ 10 регистр команд ll, счетчик команд 12, блок контроля 13, блок формирования макрокоманд 14 и устройство ввода-вывода 15.

Арифметико-логический блок 1, выполненный на однородной перестраиваемой структуре, предназначен для реализиции операторов, соответствующих командам внутреннего языка машины. Применение однородной перестраиваемой структуры позволяет в каждом цикле работы машины формировать в арифметико-логическом блоке требуемое количество операторов требуемого типа в соответствии с его ресурсами. Оперативное запоминающее устройство 2 предназначено для хранения промежуточных результатов и некоторых констант. Блок управления памятью 3 предназначен для управления обменом операндов между оперативным запоминающим устрой ством, регистрами памяти и другими блоками малой управляющей цифровой вычислительной машины. Регистры памяти 4, 5 и

6 используются для хранения и обмена операндами между арифметико-логическим блоком и устройством ввода-вывода. Блок управления 7 формирует необходимые управляющие сигналы для постоянного запоминающего устройства программ, постоянного зап< мигающего устройства команд и блока на= стройки по сигналам счетчика команд 12.

Постоянное запоминающее устройство про грамм 10 содержит константы, коды операций, адреса операндов, внешних устройств и указатель размерности обрабатываемого массива. В постоянном запоминающем устройстве команд 8 хранятся коды настройки однородной перестраиваемой структуры и параметры операторов: разрядность операндов, длительность операций. Блок настройки

9 предназначен для выбора и настройки ячеек однородной перестраиваемой структуры на различные функции в соответствии с реализуемыми операторами. В регистр команд ll записывается необходимая управляющая информация для различных блоков малой управляющей цифровой вычислитель ной машины. Блок контроля 13 осуществляет контроль и индикацию неисправностей в случае их возникновения. Блок формирования макрокоманд 14 в соответствии с указанными в команде параметрами вырабатывает серии управляющих сигналов для реализованных в однородной перестраиваемой структуре операторов. Устройство вво да-вывода 15 обеспечивает обмен информа1цией между малой управляющей цифровой вычислительной машиной и внешними устройствами.

При роботе описываемой машины в случае выполнения произвольной команды иополнение ее начинается после сигнала

Пуск, причем первый раз этот сигнал дается с пульта, а последующие команды инициируются блоком управления. Выполнение команды условно разбивается на две фазы — подготовительную и исполнительную.

Во время выполнения первой, фазы регистр команд заполняется управляющей информацией, производятся настройка однородной перестраиваемой структуры и выборка операндов, После выполнения указанных операций осуществляется вторая фаза коман-525099

30 о ды, результат выполнения которой выводится в оперативное запоминающее или на внешнее устройство. Далее формируется сигнал, аналогичный сигналу Пуск, и выполняется следующая команда.

Формула изобретения

Малая управляющая цифровая вычислительная машина, содержащая постоянное запоминающее устройство команд, счетчик команд, блок контроля и арифметикс-логический блок, информационный выход которого соединен с первыми информационными входами блока управления памятью и устройства ввода-вывода, при этом первый информационный вход арифметико-логического блока соединен с первым информационным выходом блока управления памятью и вторым информационным входом устройства ввода-вывода, а второй информационный вход соединен с первым информационным выходом устройства ввОда-вывода и вторым информационным входом блока управления памятью, третий, четвертый, пятый и шестой информационные входы которого соединены соответственно с выходами оперативного запоминающего устройства и первого, второго и третьего регистров памяти, второй информационный выход блока управления памятью соединен со входами оперативного запоминающего устройства и первого, второго и третьего регистров памяти, а первый управляющий вход соединен с первым выходом регистра команд, первый вход которого соединен с первым выходом постоянного запоминающего устройства программ, о т— л ич а ю шe.я сся а тTеeмM, что, с целью увеличения быстродействия и повышения коэффициента использования оборудования, арифметико-логический блок выполнен на однородной перестраиваемой структуре и введены блок управления, блок настройки и блок формирования макрокоманд, выход которого соединен со вторым управляющим входом блока управления памятью, а вход - co вторым выходом регистра команд, второй вход которого соединен с первым выходом постоянного запоминающего устройства команд, а третий выход подключен к первому управляющему входу устройства ввода-вывода, второй информационный выход которого подключен к первому входу блока управления, а второй информационный вход соединен с первым выходом блока контроля, первый вход которого сос динен с контрольным выходом блока управления памятью, а второй и третий входы подключены соответственно к контрольному выходу блока настройки и первому выходу блока управления, второй вход которого соединен со вторым выходом блока контроля, третий вход блока управления соединен со счетчиком команд, а четвертый вход подключен к первому выходу блока настройки, второй выход блока управления соединен с постоянным запоминающим устройством программ, второй выход которого подключен к третьему управляюшему входу блока управления памятью, третий выход блока управления соединен с первым входом постоянного запоминающего устройства команд, второй вход которого подключен ко второму выходу блока настройки, а второй выход соединен с первыъ.. управляющим входом арифметико-логическсго блока, управляющий выход которого соединен со счетчиком команд, а второй управляющий вход подключен к третьему выходу блока настройки, вход которого соединен с четвертым выходом блока управлепия.

525099

Составитель И, Хазова

Техред А. Богдан Корректор lI. Мельниченко

Редактор Л. Тюрина

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 5104/590 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д.4/5