Логарифмическое множительно-делительное устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕЕЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 03 02 75 (21) 2101564/24 с присоединением заявки ¹â€” (23) Приоритет (43) Опубликовано 15.08.76. Бюллетень № 30 (45) Дата опубликования описания 05.04.77

Союз Советских

Социалистических

Республик (и) 525121 с,. (51) М. Кл.

G 06 6 7/24

Q 06 G 7/16

Государственный комитет

Сонета Министров СССР оо делам изобретений н открытий (53) УДК

681.335 (088.8) (72) Авторы изобретения

А. М. Косолапов и В. А. Щербаков (71) Заявитель Куйбышевский политехнический институт им. В. В. Куйбышева (54) ЛОГАРИФМИЧЕСКОЕ МНОЖИТЕЛЬНΠ— ДЕЛИТЕЛЬНОЕ

УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых вычислительных машинах для выполнения операций умножения или деления.

Известно логарифмическое делительное устройство (1), содержащее синхронизирующий генератор, выход которого подключен к выходу генератора экспоненциального напряжения, компаратор и триггер, Такое устройство имеет сравнительно невысо- 1ð кую точность выполнения операции деления.

Известно также логарифмическое множительно-делительное устройство (2) содержащее коммутатор входных сигналов, логарифмический время-импульсный преобразователь и фильтр-усили- 1н тель, генератор тактовых импульсов, выход которого подключен к выходу формирователя экспоненциального напряжения и входу блока управления, выход которого присоединен к управляющему входу коммутатора входных сигналов, источник gp опорного напряжения.

Однако это устройство имеет сравнительно невысокое быстродействие и малую точность работы из-за отсутствия возможности компенсации сигналов ошибки. 25

Целью изобретения является повышение быстродействия и точности работы устройства.

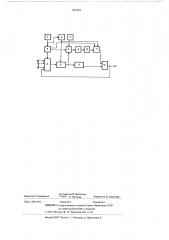

Это достигается тем, что в устройство введены последовательно соединенные интегратор, нуль-орган, блок запоминания и выходной сумматор, двухпозиционный ключевой элемент, один сигнальный вход которого соединен с выходом логарифмического время-импульсного преобразователя, а другой сигнальный вход подключен к источнику опорного напряжения, выход выходного сумматора соединен с одним из входов коммутатора входных сигналов, управляющий вход двухпозиционного ключевого элемента подключен к одному из дополнительных выходов блока управления, другой дополнительный выход которого присоединен к соответствующему входу блока запоминателя, один из входов которого соединен с выходом формирователя экспоненциального напряжения, На чертеже показана функциональная схема предлагаемого устройства.

Устройство включает в себя генератор тактовых импульсов 1, блок управления 2, коммутатор входных сигналов 3, формирователь экспоненциального напряжения 4, логарифмический время-импульсный преобразователь 5, двухпозиционный ключевой!

:,)), Гс, ) !

))с,,;с. )!3.), i; с (О. с.:).01, с. с 1.

К11Х ЬХ1). !1.Ь.Х 011. 1" ) : . с!

О) ь) л - « -" . i. )!с " *!

ПОрт):!Она.:,Ьла П )с)с. ЭЬС. .;- :;) );, .",.-, !. (!),:-;,а, С1 Г)1!)»10Гс.

10ЧНВЯ С.1011)111)).!1 )-;! .1, )т ..",;; Сс!" .. " " " ) - . »)Ч!) ..."

))011)!)!110 Тj ) jV) ) - ;.!,.,,"..".„. . (J -) ), .) 1(,С))С

Запа А!) 11а1сс) " : И; с . 1): » ", 1 аа 12 па акоп-сании переходного процесса устанавs.::,)чается точное "";íÿ÷åíI)å результата операции.

Так ка)с следя)цая система отслеживает не весь

1:с:зуг1ьтат преобразования, а только величину ошиб;:.)„").0 пр;:. тай же статической ошибке некомпенсании следящей системы коэффициент передачи с,,))111ьтра-усилителя может быть уменьшен в число !

)11З„)01ТРЕДЕЛЯСМОЕ )ОТНОШЕНИЕМ ВЫХОДНОГО НаПРЯжЕ-)1)11,:,;райства;, Выхода Выходного сумматора 12 к

Величине !)и)))бки преабразован1я, а это, в свою с"i:,,"!;!11), п1) Jol)ji,!ст D i заданном у1)Овне пульсаций га в ыхаде ) 0!райства соответственно во столько же !. аз уменьшить .састаяннук) Времени фильтра-усили" тсля ":-, что позволяет увеличить быстродействие

01!сто.;.)Ь1 при тай же;.Очности преобразования.

1аки. .т оаразам) метрологические характеристи: ;;-:!)ã0 устрайс1В"=. Определяются точностью логас)и!1))!щ.еского Время-импульсного преобразователя, -","с:1) аде)1 от)111е ..;;ох cò быть увеличено В десятки !

) аз .:;). счс-;. примана)11)а про "тога блока запоминания, :"v, ь с,".-! g!!!! ..1нте )) .;тара и !,Вуупоэицианнага ключе!

)!Ор;.)ул из05ре ения.. Ога:=)ифми-)еское множительно-целительное у):).ройст),!), садержагдее последовательно соединен11ь!с:.Ом. :.«)та::o! Входных сигналов, логарифмичес,-::и".:,,«p;-.)01-Ijмлулы)ный преобразователь и фильтрга", i 0! с гв- - .Е))а 0 ТВКТОВЫХ ИМПУЛЬСОВ) ВЫХОД

: . „Ра га; —. О Э»Е)! се ВХОДУ фа РМИРОВатЕЛЯ, ..=.",:1«÷è;.;,.-Лаг1) пагряжения и вхоцу блока

)Г);!В))ЕННЯс ЛЬ1=,0)). КОТОРОГО ПРИСОЕДИНЕН К УПРав.:;.;лт,халу КО!и!мутатора Вхоцных сигналов, . ): . (. )! .":;; i;) плата 1 !IP)IÆCIÈß, 0 T Л И Ч а Ю Ig Е C С Я

;, О, )) Ill ;. i; „« „(0)«4IHIGI5iR ОыстРОДеЙствиЯ H Io)IВ Нс ГС ) .ÇñДЕБЪ«ПО СЛЕДОВ аТЕЛЬНО СОЕДИ:;,;: ь с ннтсгра,ар, нуль-орган, блок запомина .Ь;Хo:.i J..)A Су)М)матар) двуХПОЗИцИаННЫй ..:.:: )-.";.JJ) !.:))!еь«е -!i . 0; Yi ) сигнальныи ВхОд кОтОра:с)Ь." .с)ДОVi ЛОГВРПфМИЧЕСКОГО ВРЕМЯ1с,,,:.::;Ьспаго нрссбраз«ователя, а другой сигналь)10)) .:.::О-))-слючен к источнику опорного напря-.е:„.Ьаа)д выходного сумматора соединен с ,.:.... .„,: )10 зь)ходов каь1мутатара входных сигналов, ;р--.)âë:IJJ):.û!)j Вход двухпозиционного ключевого :! Мента )10! Люнен к Одному из дОполнительных

-. . !отса)З бпаха «П!раВЛЕНИя) друГОй дОПОЛНИтЕЛЬ.ь и )ых1)дкатарага подсоединен к саатветствуюшевхаду блока запоминания, один из входов

:-:.."араго соедиьен с выходом формирователя эк;;,; онснциального напряжения. .":;, .; 111ИКИ ЯпфаРМапии, ПРИсГЯтЫЕ Ва ВНИМаНИЕ

" н капе!)сн)зе изабРетениЯ.

;: . !саг)уп1))э Во)энико вые код-руи1цие и декодирую:;1)J;; преабра. онат ли на1тряжения. 11ад ред. B,Б.Смонергия 1967 r c. 283;с )1

2., .,1)т.св "148352 кл, Е 02 В 8/02,опубл.21.09.61.

525121

Составитель И. Шелипова

Техред О.Луговая

Корректор Н. Бугакова

Редактор Н. Каменская

Заказ 5091/591

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5